摘要:根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台上设计实现了BPSK调制信号载波频率估计单元。利用ModelSim仿真环境对载频估计功能进行仿真,验证了平方倍频法对BPSK信号进行载波信号估计的有效性。仿真表明基于FPGA的BPSK信号载频估计单元,有较高的估计精度,且实现原理简单,有一定的实际应用价值。

0 引言BPSK即二进制相移键控,是直扩信号中经常使用的一种调制方式,利用载波的相位变化传递数字信息,信号的振幅、频率保持恒定。BP SK调制方式具有较高传输效率、误码率低,不易受信道特性变化影响等特点,而且调制电路简单易行,频谱密度低,处理增益高,具有良好的低截获概率可能,广泛应用于雷达、保密通信和导航定位等领域。对BPSK信号的载频估计为后续的跟踪捕获等处理提供载频参数,具有重大意义。随着信号处理技术和检测技术的飞速发展,涌现出了很多估计载波频率的方法,如平方倍频法、小波相关法等。

本文根据BPSK调制信号调制机理和平方倍频法原理,在FPGA平台下对基于平方倍频法的BPSK调制信号载频估计单元进行设计,并在Mode lsim6.5b环境下进行仿真验证和结果分析。

1 平方倍频法频率估计原理

BPSK调制信号用初始相位0和π分别表示二进制“1”和“0”,BPSK信号的时域数学表达式可以表示为:

Sbpsk(t)=A·D(t)cos(2πft+φ) (1)

式中,A代表振幅,D(t)代表二进制信息,将D(t)与载波相乘,因D(t)只有两种值,即“+1”和“-1”,分别代表“0”和“1”,使得BPSK调制信号只有两种相位,则BPSK调制信号的生成原理图如图1所示。

根据BPSK的调制原理,利用二进制信息对载波信号进行相位调制,使载波信号相位突变,即BPSK信号同时含有载波信息和二进制信息。因此对BPSK调制信号的载频估计应该首先将二进制信息造成的相位突变消除,只留下载波或与载波有关的成分,再进行载频估计。因为BPSK调制信号的二进制信息是±1构成的序列,可以用平方处理消除二进制信息的影响,提取其中仅与载波有关的成分进行载波频率估计。

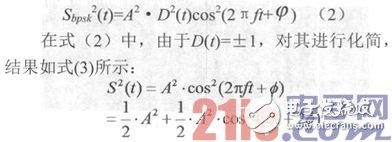

BPSK调制信号的数学表达式如式(1),对其平方,结果如式(2)。

由式(3)可知,平方后信号中包含BPSK调制信号载频信号的平方项和直流分量。对平方结果进行傅里叶变换,求其频谱,搜索频谱峰值,并将谱峰位置输出,则可以得到2fc的估计值,最后除以2即可得到BPSK调制信号的载波频率。

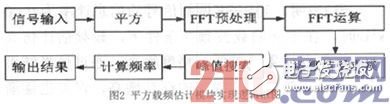

2 基于FPGA的载频估计单元设计载波频率估计单元首先实现对BPSK调制信号进行平方处理,然后将平方后的信号进行快速傅里叶变换(FFT),对频域进行二倍频的频域采样点输出,最后通过FFT变换的频率分辨率与输出采样点的比例关系完成载频的估计。

载频估计单元实现逻辑框图如图2所示。

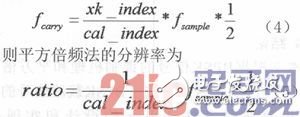

其中,FFT运算点数为cal_index,采样频率为fsample,而峰值所在位置为xk_index,而峰值所在位置是载波二倍频所在位置,则载波频率fcarry的计算公式为:

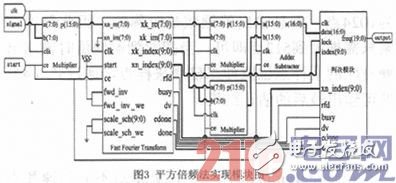

根据以上分析,对载频估计模块的设计主要分为四部分:乘法器、FFT单元、平方求和单元、判决单元。根据平方倍频法原理以及逻辑框图2,在FPGA平台上设计的载波频率估计单元FPGA结构如图3所示。

表1为图3中的载频估计单元的输入输出接口,以及各个接口实现的功能。

图3中所设计的载频估计模块采用的算法是平方倍频法,根据平方倍频法原理,对输入信号首先要进行平方处理。本单元使用XilinX公司提供的MulTIplier IP核,版本为4.0。MulTIplier IP核的两个输入信号为8位的有符号定点数,输出信号是16位的有符号定点数。将平方后的信号进行傅里叶变换之前,需要对信号进行预处理。图3中所示的载频估计单元的关键模块是傅里叶变换模块。本单元使用的傅里叶模块是由Xilinx公司提供的Fast Fourier Transform IP核,版本号为7.1。该IP核要求输入数据为复数形式,因为通过乘法器计算后的数据是实数,因此对数据的预处理是加上一个为0的虚部,同时为了减少傅里叶变换的计算量,减少计算时间,这里将输入数据进行截短,只留数据的前8位,然后传送给Fast Fourier transform IP核进行计算。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)