我们知道XDC与UCF的根本区别之一就是对跨时钟域路径(CDC)的缺省认识不同,那么碰到FPGA设计中常见的CDC路径,到底应该怎么约束,在设计上又要注意些什么才能保证时序报告的准确性?

CDC的定义与分类CDC是Clock Domain Crossing的简称,CDC时序路径指的是起点和终点由不同时钟驱动的路径。在电路设计中对这些跨时钟域路径往往需要进行特别的处理来避免亚稳态的产生,例如使用简单同步器、握手电路或是FIFO来隔离。

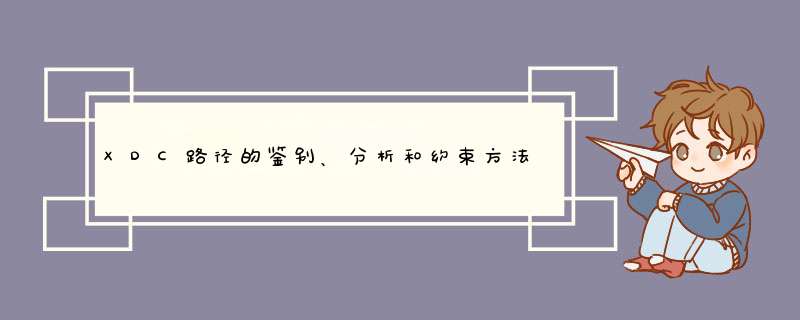

安全的CDC路径所谓安全的CDC路径是指那些源时钟和目标时钟拥有相同的来源,在FPGA内部共享部分时钟网络的时序路径。这里的安全指的是时钟之间的关系对Vivado来说是全透明可分析的。

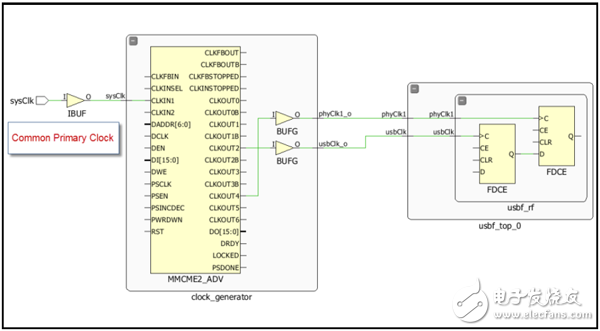

不安全的CDC路径则表示源时钟和目标时钟不同,且由不同的端口进入FPGA,在芯片内部不共享时钟网络。这种情况下,Vivado的报告也只是基于端口处创建的主时钟在约束文件中所描述的相位和频率关系来分析,并不能代表时钟之间真实的关系。

在ISE中想要快速定位那些需要关注的CDC路径并不容易,特别是要找到不安全的CDC时,因为ISE缺省认为所有来源不同的时钟都不相关且不做分析,要报告出这类路径,需要使用ISE TIming Analyzer (TRCE) ,并加上 “-u” (表示unconstrained)这个选项。

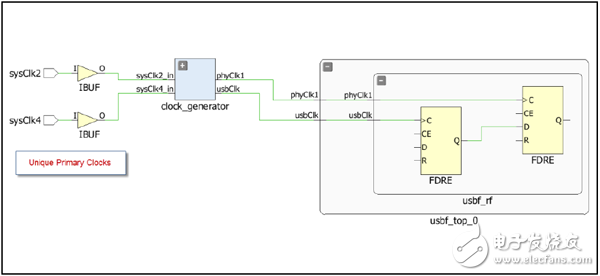

在Vivado中则容易许多,我们可以使用report_clock_interacTIon命令(GUI支持)来鉴别和报告设计中所有的时钟关系。执行命令后会生成一个矩阵图,其中对角线上的路径表示源时钟与目标时钟相同的时钟内部路径,其余都是CDC路径。

Vivado还会根据网表和已读入的约束分析出CDC路径的约束情况,并分颜色表示。例如绿色代表有时序约束,红色代表不安全的CDC路径但是没有约束时序例外,橙色表示有部分路径已约束为false path的不安全CDC路径。

矩阵下方是时钟关系表格,可以就各种条件进行筛选和排序,方便定位CDC路径。建议的做法是:首先,对“Common Primary Clock”排序(显示为Yes 或No),这么做可以快速鉴别出那些安全和不安全的CDC路径,接着观察对应的“Inter-Clock Constraints”栏内的内容,判断已读入的XDC中是否对这类路径进行了合理的约束。

第二步,可以对“Path Req (WNS)”由小到大进行排序,找到那些数值特别小(例如小于100ps)或是显示为“Unexpanded”的CDC路径,结合是否共享“Common Primary Clock”来鉴别此类路径,作出合理的约束。

过小的Path Req (WNS)一般都表示此类跨时钟域路径缺少异步时钟关系或其它时序例外的约束,如果两个时钟连“Common Primary Clock”也不共享,则100%可以确认为异步时钟,应该加上相应的时钟关系约束。

显示为“Unexpanded”的时钟关系,表示Vivado在一定长度(缺省为1000)的周期内都没有为两个时钟的频率和相位找到固定的关系,则无法推导出相应的Path Req 约束值。此类CDC需要特别留意,也要加上异步时钟关系约束。

这个矩阵还支持交互式的时序分析,选中任意一个方框,右键显示下拉菜单:选择Report TIming,会报告出这一格代表的时钟域(本时钟域或是跨时钟域)内最差的时序路径;选择 Set Clock Groups则可以设置时钟关系约束并添加到XDC文件中。

CDC的设计与约束CDC路径在FPGA设计中普遍存在,在设置相应的约束前,必须了解设计中采取了怎样的方法来处理跨时钟域路径。

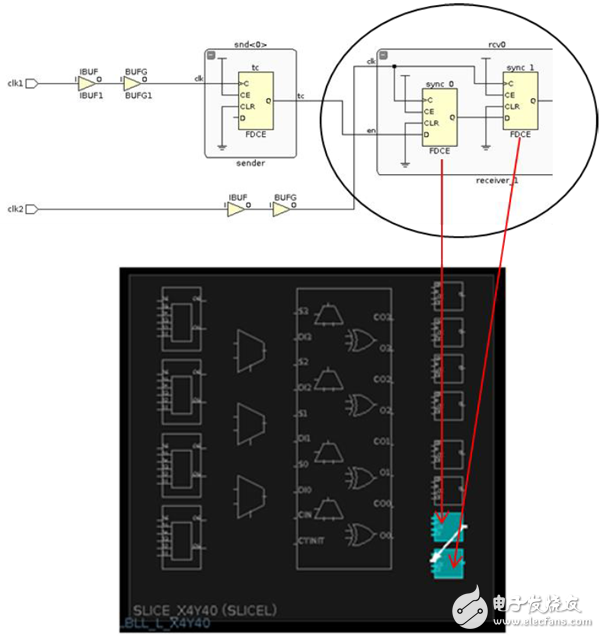

简单同步器对于单根跨时钟域路径,一般采用简单同步器(Simple Synchronizer),就是由至少两级CE端和Reset/Clear端接死的寄存器序列来处理。

这种情况下,为了更长的平均无故障时间MTBF(Mean TIme Between Failures),需要配合一个ASYNC_REG的约束,把用作简单同步器的多个寄存器放入同一个SLICE,以降低走线延时的不一致和不确定性。

set_property ASYNC_REG TRUE [get_cells [list sync0_reg sync1_reg]]

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)