NI LabVIEW FPGA模块帮助DAQ系统的开发者灵活自如地进行应用程序编程以实现各类输入/输出 *** 作。 用户无需预先了解VHDL等硬件设计工具,便可将LabVIEW代码嵌入FPGA芯片并获得硬件定时的速度和可靠性。

让我们先从数据采集硬件的常用组件切入论题。 假设您拥有了模数转换器(ADC)、数模转换器(DAC)和数字输入/输出线,则所有I/O便要根据实际 *** 作接受某种方式的定时和控制。 典型的多功能数据采集设备采用功能齐全的ASIC,满足了大多数的功能性需求。 比如:M系列DAQ设备通过DAQ-STC2,控制着各类硬件组件的定时和触发。 智能DAQ硬件(如:R系列DAQ设备)区别于市面上的其他任何数据采集设备,因为在控制设备功能方面智能DAQ用基于FPGA的系统定时控制器取代了传统ASIC,从而使得所有模拟和数字I/O都能根据特定应用 *** 作接受相应的配置。 可重配置FPGA芯片通过NI LabVIEW FPGA模块进行编程,此时NI LabVIEW的数据流模式仍旧适用,不过采用了一组新函数控制最底层的设备I/O。 LabVIEW FPGA I/O节点并不通过NI-DAQmx函数负责实现常见的任务和功能,而是灵活自如地在各个通道最底层上运行。 通过以下各部分的内容,我们将了解NI-DAQmx的特定实例,并学习如何通过智能DAQ定制各类数据采集任务。

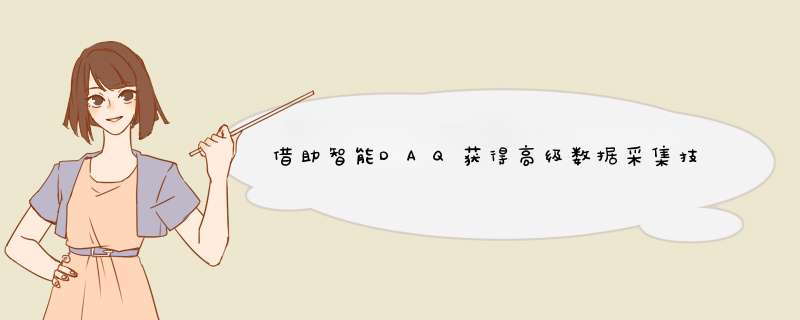

2. 定时和触发实现高级数据采集的智能DAQ主要用于定制定时和触发。 下方的范例程序框图展现了:NI-DAQmx帮助实现的触发式模拟输入任务。

图1. 通过NI-DAQmx实现的触发式模拟输入

如图1所示,智能DAQ并未使用不同函数配置通道,而是通过名为I/O节点的函数读写各路模拟和数字通道。 让我们看看使用NI LabVIEW FPGA中I/O节点所获得的相同功能。

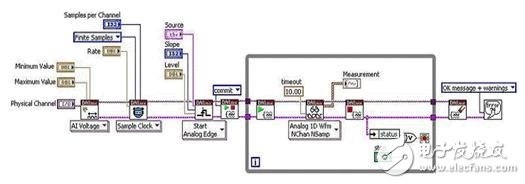

图2. 通过智能DAQ和NI LabVIEW FPGA实现的触发式模拟输入

上图既没有针对全局通道、采样时钟、触发的配置函数,也没有开始、停止和清除等任务。 所有内容都被1个简单的模拟I/O读取所取代;全部定时都为本地LabVIEW结构(如:While循环和条件结构)所控制。由于整个程序框图均在FPGA硬件内执行,LabVIEW代码的运行便体现出硬件定时的速度和可靠性。 让我们更深入地了解一下该程序框图的运行方式。 模拟I/O节点并不指定某个采样速率,而使用For循环采集各个样本。 与之对应的ADC在I/O节点被调用时,负责对输入信号进行实际数字化,因而通过For循环接受定时。 若想在100 kHz的频率下进行信号采样,针对循环的延迟就必须设定为10 µs。 循环的定时器函数从第2轮循环迭代开始便确保着特定的时间延迟,用户因而能够通过顺序结构保证样本之间存在着指定的时间间隔。 NI LabVIEW FPGA中功能强大的条件结构,实际代表了用于封装各类代码的硬件触发。 由于所有的函数和结构都通过逻辑单元在硬件内运行,所以条件结构确保开始具有实时10 µs时间精度的采样。 最后需指出的是,由于 *** 作位于硬件层,只涉及几个层次的抽象处理,因此用户无需清除任务ID或释放内存。

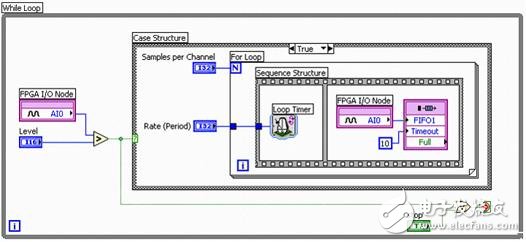

就基于FPGA的智能DAQ硬件而言,其真正的优势是能够定制各类定时和触发,并在硬件中进行信号处理和决策。 现在让我们了解一下:针对某类自定义应用,需对模拟输入触发做出哪些修改。 若我们希望在2路模拟输入通道的某路电压超过指定范围时便触发采集,又该如何修改呢? 借助NI LabVIEW FPGA,此类任务的执行易如反掌。

图 3. 通过智能DAQ和NI LabVIEW FPGA实现的自定义触发式模拟输入

这里,我们已经为程序框图添加了第2个I/O节点和第2个比较函数,以及1个布尔“或”函数。 智能DAQ硬件为所有的模拟输入通道提供专用ADC,因而2路通道能够接受同步采样;同时,只要任何1路通道的电压超过了指定范围,条件结构便会执行“真”条件,并开始以10 µs时间精度进行采样。 请记住:缺少智能DAQ便不可能生成类似的触发;在其他DAQ硬件上应用时,触发需要具有更高延迟的软件定时来实现。 如果此后我们希望通过扩展将监控范围从2路通道延伸至全部8路通道,甚至希望添加数字触发,就需要简化自定义代码。 添加预触发扫描后,用户便可对输入通道不断进行采样并将数据传送至FIFO缓冲器。 触发器一旦接受读取,FIFO缓冲器和此后的采样便可经由DMA通道,被传送至主机。

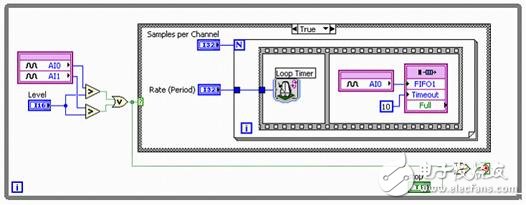

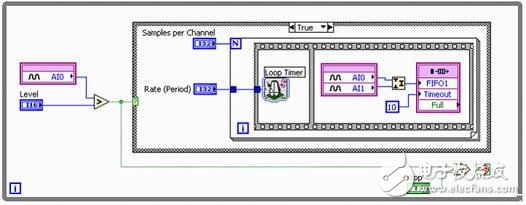

如果我们希望借助NI-DAQmx驱动,对第2模拟输入通道进行采样,则该程序框图与图1所示的内容相差无几。然而限制依然存在,因为2路通道均被迫引用相同的触发器并以相同的时钟频率进行采样。 现在我们来看看:智能DAQ和NI LabVIEW FPGA帮助实现的各类多通道采样。

图4. 通过智能DAQ实现的触发式同步模拟输入

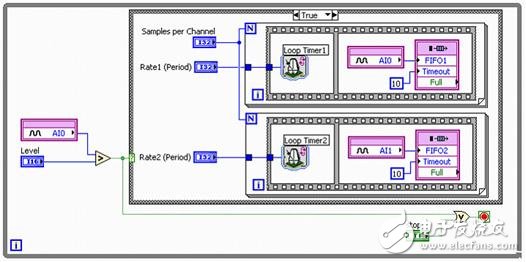

图4(上图)展现了:如何基于模拟输入通道0中的模拟触发器,对2路不同的模拟输入通道进行同步采样。由于智能DAQ设备均配有独立的ADC,在同一I/O节点中的2路通道可在完全相同的时刻接受采样。 典型的多功能DAQ设备可通过一个ADC多路复用所有通道,因此,各路通道必须共享相同的采样时钟和触发线。 图5(下图)展现了:智能DAQ硬件其实能够以独立的速率,对不同的模拟输入通道进行采样。 在独立回路中放置模拟输入I/O节点后,每路通道会以完全不同的速率进行采样,然后各自通过2条DMA通道读写硬盘。

图5. 通过智能DAQ实现的触发式多速率模拟输入

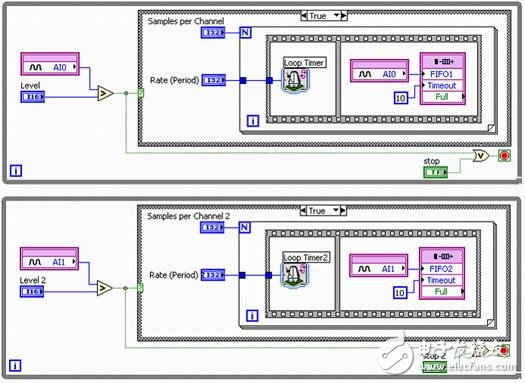

最后需指出的是,我们若是希望2路通道具有相互独立的采样率和开始触发,则可参照图6,将所有I/O节点都部署在并行循环结构中。该方式充分利用了FPGA的并行性,确保了各项任务能够使用专用资源并在执行时完全独立于其他采集任务。

图6. 通过智能DAQ实现的独立触发式多速率模拟输入

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)