验证RTL模块或FPGA是否满足要求可能颇具挑战。但有些方法可用来优化验证流程,以确保验证成功。

验证FPGA或RTL模块可能是一个非常耗时的过程,因为工程师要极力确保设计能够按照规范要求并在可能导致模块错误的极端状况下正确运行。工程师通常采用测试平台来达到验证目的,测试平台是一种为测试设计而创建的文件。然而,测试平台可简可繁。下面,就让我们来了解一下如何充分利用测试平台,而又不会使其过于繁琐。

什么是验证?

验证是指确保被测单元(UUT)同时满足设计要求和设计规范,适合其预期目的。很多情况下是由独立于设计团队之外的团队来执行验证工作,对项目有个全新的认识。这样,设计UUT的人并非是断定其能否正确工作的人。

鉴于现代FPGA设计的尺寸之大、复杂程度之高,要确保UUT按规范运行可能是一项艰巨的任务。因此,工程设计团队必须在项目初期确定采用哪种验证策略。选择策略技巧如下:

. 仅功能仿真——该技术检查设计是否正确运行。

. 功能仿真和代码覆盖率——该方法在检查功能正确性的同时,还要检查设计中所有代码是否都经过测试。

. 门级仿真——该技术同样验证设计的功能性。当用来自最终实现的设计的时序信息进行后端注释时,执行这种仿真方法会耗费大量的时间。

. 静态时序分析——该方法对最终设计进行分析,以确保模块达到时序性能。

. 形式等效校验——工程师使用该技术检查网表与RTL文件的等效性。

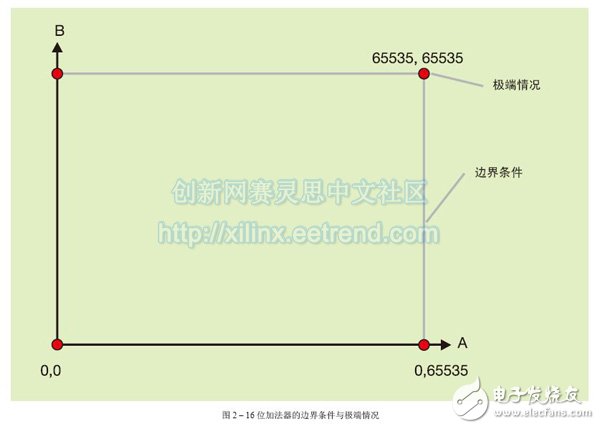

边界条件是指输入中有一个达到极值,而极端情况是指所有输入均达到极值。

无论使用哪种验证策略,工程设计团队都需要制定一个测试计划,规定如何对每个模块和最终FPGA进行验证并满足所有要求。

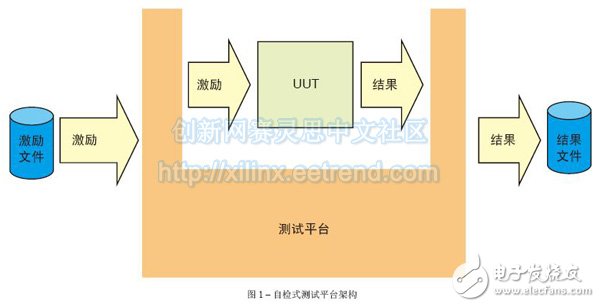

自检测试平台

为激励UUT而创建的测试平台既可以是自检式也可以是非自检式。如果您倾向于使用非自检式,那么需要用肉眼观察电脑显示器上的测试结果,以确定测试平台能够按预期工作。而自检式测试平台与传统测试平台的区别在于,除了施加激励外,还要依照预期结果对UUT的输出进行检查,如图1所示。这样就可以明确地说明UUT是否通过测试。将该功能与通过文本文件的控制与汇报功能相结合,就能创建一种功能非常强大的验证工具。

自检测试平台具有多种优势。首先,用肉眼验证仿真波形的这种方法非常耗时而且极其复杂,而自检测试平台则能为您省去这种人力成本。此外,自检测试平台还能提供综合而全面的通过或是失败报告,您可在后续的设计流程中将其作为测试凭证保存并使用。若UUT需要在后续阶段进行设计迭代,那么返回测试平台并确定测试是否通过或失败(该流程通常称为回归测试流程)所需的时间就会远远少于采用传统测试平台所耗费的时间。

极端条件、边界条件和应力测试

使用测试平台的目的是确保模块按照功能要求执行,任何极端状况都能得到解决,同时,最重要的是测试平台应充分执行UUT代码。因此在验证设计模块时,经常用到“玻璃盒”测试法,因为这样可以了解和观察UUT模块的内部情况。相比之下,当UUT为FPGA时,由于顶层需要更长的验证与仿真时间,您需要使用顶层的黑盒测试法。

为了根据要求验证设计的功能性,测试平台所应用的激励必须与模块预期在运行中能看到的激励相同。然而,测试所有可能的输入以证明功能合规性可能是一个非常耗时的过程。因此,工程师会将重点集中在边界条件和极端情况上,并测试一些典型 *** 作值。

边界条件是指输入中有一个达到极值,而极端情况是指所有输入均达到极值。能较好体现这两种情况的实例是简单的16位加法器,用于累加两个数值并得出结果。图2给出了这种情况下的边界条件和极端情况。

您可以清楚地看到,极端情况是当A和B输入都等于0;当A等于0,B等于65535;当A和B都等于65535;以及当A等于65535,B等于0。边界条件是极端情况之间的值。

对于有些应用,可能要对UUT进行应力测试,以确保在正常运行之外有一定的裕量。应力测试会根据模块而变化,但可能涉及重复 *** 作,从而使缓冲器和FIFO溢出。对设计采取应力测试可减少验证工程师损坏UUT的几率。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)