目前市面上有多种数据采集卡,但其应用都具有一定的局限性,不可能完全满足用户的需求。本文介绍的数据采集卡可应用于某视频图像采集系统中,数据源发送多路同步串行数据,然后经过数据采集卡传入上位机用以进行后续分析。上位机向外写控制字并转换后以异步串行方式输出。用以控制视频图像的采集。本系统将PCI接口逻辑和其他用户逻辑集成于一片FPGA中,因而大大节省了资源,便于进行串口扩展及其他功能的添加,性能良好,用途广泛。

1 PCI总线

PCI总线是一种高性能的局部总线,具有32位可升级到64位的、独立于CPU的总线结构。工作频率为33/66 MHz,最高传送速度可达132 MB/s(32位、33 MHz)或528 MB/s(64位、66 MHz)。

PCI总线定义了Memory(存储器)空间、I/O(输入/输出)空间和配置空间3种地址空间,并具有两种工作模式:其中主模式下的PCI设备具有总线控制权,可以实现DMA传输;而被主设备控制进行通信的称为从模式(TARGET)。

1.1 PCI总线的配置空间

所有的PCI设备都必须实现配置空间,该空间分为首部区和设备有关区。首部区中的强制性寄存器有:供应商代码(Vendor ID)寄存器用于标明设备制造商),设备代码(Device ID)寄存器(用于指明特定的设备,它由供应商分配),版本识别(Revision ID)寄存器,首部类型(He-ader Type)寄存器和类别寄存器(Class Code)。以上五个寄存器均可用于PCI总线上设备的识别。另外,首部区中还有两种必须实现的寄存器:其中命令寄存器用于存放PCI命令,而设备状态寄存器则用于记录PCI的状态信息。

*** 作系统在启动时应判断系统中有多少存储器、以及I/O设备需要多少地址空间,然后建立统一的地址映射关系,这时的PCI设备需要用到基地址寄存器。另外,若要实现中断,还必须设置中断引脚(Interrupt Pin)寄存器和中断线(Interrupt Line)寄存器。

1.2 PCI总线的中断机制

PCI总线的硬件中断方式分为边沿触发和电平触发,PCI设备为低电平触发(level-sensiTIve)。PCI总线上有4条中断请求信号线:INTA ,中断引脚寄存器的值01H~04H分别对应4条中断线,单功能PCI设备只能使用INTA#。此外,使用了中断引脚的设备还必须实现中断线寄存器。POST例程(加电自检测程序)在进行系统初始化和配置时还要将中断线信息写入该寄存器。PCI总线中断是可以共享的,这一方面解决了中断资源紧张的问题,但另一方面也会给PCI中断的实现带来麻烦。

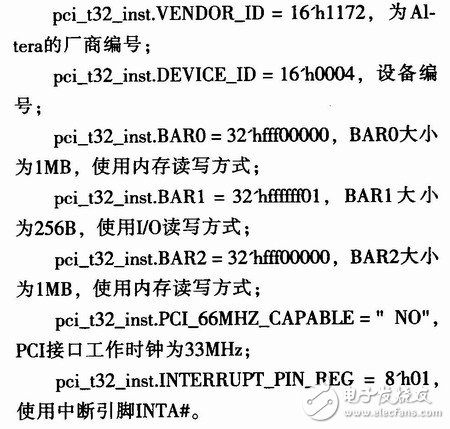

2.1 PCI配置寄存器的设置

Altera公司的PCI编译器(PCI Compiler)提供有使用Altera器件实现PCI接口设计的完全解决方案。其中包括4种PCI接口兆核函数(PCI IP)及相关测试平台。

通过PCI编译器的IP工具台或直接编辑生成的兆核函数头文件可以设置并修改PCI的配置空间信息,本系统的主要配置信息如下:

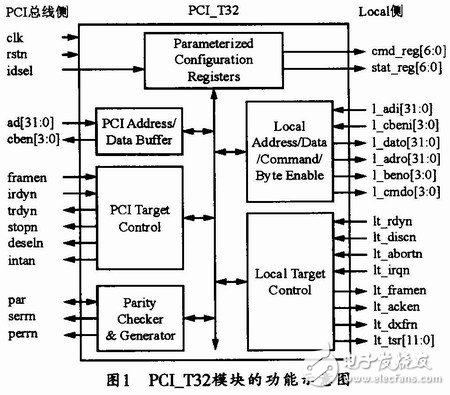

2.2 PCI T32兆核函数的内部结构及外围信号

PCI Compiler提供的四种PCI IP包括PCI_M64/32、64/32位的主模式接口和PCI_T64/32、64/32位的从模式接口。本系统通过PCI接口与PC机传输32位数据,并由上位机应用程序控制系统工作。故该系统工作于32位从模式,即本系统的PCI接口使用PCI_T32模块来实现,该模块的内部功能及外围信号如图1所示。

参数配置寄存器(Parameterizde ConfiguraTIon Registers)是符合PCI规范的所有配置的寄存器,可用于识别设备、控制PCI总线功能、提供PCI总线状态等,PCI侧从模式控制模块(PCI Target Control)用于控制PCI_T32与PCI总线的各种 *** 作,而用户侧从模式控制模块(Local Target Control)则用于控制PCI_T32与用户逻辑的各种 *** 作。

PCI_T32上PCI总线一侧的信号是符合PCI协议的标准信号,该信号Local侧的信号为Altera PCI IP特有的与用户逻辑接口的信号,起着关键作用。其中:

l_adi[31:0]为地址/数据输入信号;

l_dato[31:0]为数据输出信号;

l_adro [31:0]为地址输出信号,读 *** 作时,可将PCI侧地址/数据信号AD[31:0]上的第一个有效周期(即地址期)的数据输出;

l_emdo[3:0]为命令输出信号,其位定义及时序符合PCI规范,其为0010时为I/O读 *** 作,为0011时为I/O写 *** 作、为0110时为内存读 *** 作。为0111时为内存写 *** 作,为1010时为配置空间读,为1011时为配置空间写,用户对这组信号进行译码可知其当前PCI总线上设备的 *** 作情况;

l_irqn为用户中断请求信号,由于PCI总线为低电平中断,所以,用户逻辑若要发出PCI中断请求,就必须将低脉冲送入l_irqn。实验证明,低脉冲持续时间须在4~8μs之间,持续时间过短会出现丢失中断现象,而时间过长时, *** 作系统又会重复响应同一个中断请求;

l_tsr[11:0]可用于控制local目标设备状态寄存器,其中D0~D5位分别对应BAR0~BAR5,哪位有效代表哪个BAR被选中;

l_dxfrn为输出信号,表示local目标设备数据传输成功。

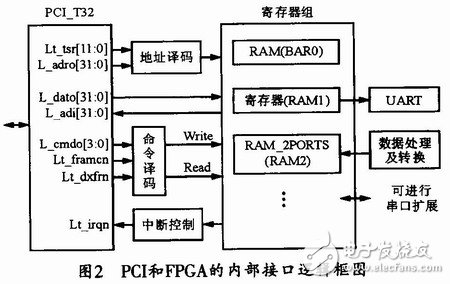

2.3 FAGA逻辑设计

一个数据采集系统若要稳定可靠地采集数据,都需要设置合适的数据缓冲区,本系统的数据缓冲区由FPGA内部IP核实现。图2所示为FPGA内部的PCI接口及数据缓冲区框图。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)