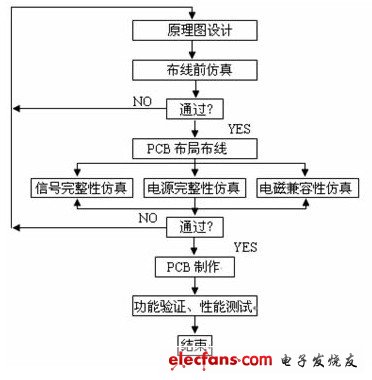

如图是传统的设计方法,在最后测试之前,没有做任何的处理,基本都是依靠设计者的经验来完成的。在对样机测试检验时才可以查找到问题,确定问题原因。为了解决问题,很可能又要从头开始设计一遍。无论是从开发周期还是开发成本上看,这种主要依赖设计者经验的方法不能满足现代产品开发的要求,更不能适应现代高速电路高复杂性的设计。所以必须借助先进的设计工具来定性、定量的分析,控制设计流程。

随着信息宽带化和高速化的发展,以前的低速PCB已完全不能满足日益增长信息化发展的需要,人们对通信需求的不断提高,要求信号的传输和处理的速度越来越快,相应的高速PCB的应用也越来越广,设计也越来越复杂。高速电路有两个方面的含义,一是频率高,通常认为数字电路的频率达到或是超过45MHZ至50MHZ,而且工作在这个频率之上的电路已经占到了整个系统的三分之一,就称为高速电路;二是从信号的上升与下降时间考虑,当信号的上升时小于6倍信号传输延时时即认为信号是高速信号,此时考虑的与信号的具体频率无关.高速PCB的出现将对硬件人员提出更高的要求,仅仅依靠自己的经验去布线,会顾此失彼,造成研发周期过长,浪费财力物力,生产出来的产品不稳定。

高速电路设计在现代电路设计中所占的比例越来越大,设计难度也越来越高,它的解决不仅需要高速器件,更需要设计者的智慧和仔细的工作,必须认真研究分析具体情况,解决存在的高速电路问题.一般说来主要包括三方面的设计:信号完整性设计、电磁兼容设计、电源完整性设计.

在电子系统与电路全面进入1GHz以上的高速高频设计领域的今天,在实现VLSI芯片、PCB和系统设计功能的前提下具有性能属性的信号完整性问题已经成为电子设计的一个瓶颈。从广义上讲,信号完整性指的是在高速产品中有互连线引起的所有问题,它主要研究互连线与数字信号的电压电流波形相互作用时其电气特性参数如何影响产品的性能。

传统的设计方法在制作的过程中没有仿真软件来考虑信号完整性问题,产品首次成功是很难的,降低了生产效率。只有在设计过程中融入信号完整性分析,才能做到产品在上市时间和性能方面占优势。对于高速PCB设计者来说,熟悉信号完整性问题机理理论知识、熟练掌握信号完整性分析方法、灵活设计信号完整性问题的解决方案是很重要的,因为只有这样才能成为21世纪信息高速化的成功硬件工程师。

信号完整性的研究还是一个不成熟的领域,很多问题只能做定性分析,为此,在设计过程中首先要尽量应用已经成熟的工程经验;其次是要对产品的性能做出预测和评估以及仿真。在设计过程中可以不断积累分析能力,不断创新解决信号完整性的方法,利用仿真工具可以得到检验。

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

Cadence公司针对PCB SI发布一个功能非常实用的高速电路设计及信号完整性分析的工具选件——Allegro PCB,利用这个仿真软件能够根据叠层的排序,PCB的介电常数,介质的厚度,信号层所处的位置以及线宽等等来判断某一PCB线条是否属于微带线、带状线、宽带耦合带状线,并且根据不同的计算公式自动计算出信号线的阻抗以及信号线的反射、串扰、电磁干扰等等,从而可以对布线进行约束以保证PCB的信号完整性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)