科学与工业研究理事会(CSIR)和Plunify公司的工程师们告诉您,他们是如何用云计算来分析大型Virtex-6设计的实现选项和用户约束的。

随着FPGA器件尺寸的增大及其内部设计密度的提高,时序收敛面临着前所未有的挑战。由于各种实现工具都竞相满足这种更高复杂性需求,把不同的实现转入量产时间越来越长[1]。为了加快速度,有些设计人员希望能通过云计算来比较分析使用不同实现选项和用户约束决策的效果。

最近,我们在南非的科学与工业研究理事会(CSIR)完成了这样一个分析过程。我们采用Plunify公司的云加速芯片设计方法为我们的设计找到了既能提供最短实现运行时间又能得到最佳时序评分的各项参数。在深入探讨我们的分析细节以及我们所使用的工具前,让我们先来了解一些背景资料。

开发板升级

在最近的一个项目中,我们需要将驻存的赛灵思Virtex-5 FPGA更换为新一代Virtex-6器件,从而升级现有的开发板。第一块开发板出现了几大问题,其中最重要的就是对于目标应用来说其管脚并不是最理想的,而且器件尺寸过小,不能满足系统需求。

我们已经拥有了运行新型开发板所需的大部分RTL代码,因此在这方面占有绝对优势,从而可对在PCB电路图设计的管脚分配阶段做出的决策进行分析。由于FPGA设计的实现运行时间较长,我们不得不限制在PCB设计阶段中执行的构建次数,从而做出决策。

在设计的硬件测试阶段,我们增加了一些原Virtex-5开发板没有的功能。不出所料,这为布局布线工具创建了更多的工作,因而我们进行了详细的布局规划演练,同时完成了大量运行,以找到最佳种子布局(placement seed)。我们决定使用Plunify公司的云实现服务来管理我们所需的大量运行。

FPGAAccel是一种软件应用程序界面(API),有助于您在远程服务器上同时定义、分配和执行FPGA综合及布局布线构建。

四个约束集

由于 Plunify服务所提供的处理功能,我们决定用四个不同的约束集分析我们的最终设计。

前两个约束集共享同一管脚,其中第一个约束集不包括布局规划,第二个则包括详细的布局规划。我们为这两个约束集选择的管脚能够重现我们在第一版开发板上所遇到的管脚分配不当造成的后果。而另外两个约束集则采用新版开发板上器件的管脚;同样,其中一个约束集不包括布局规划,另一个包括详细的布局规划。

我们需要用这些约束集来验证对FPGA 管脚的更改是否真的会影响时序收敛,以及仅在第一版开发板上改变种子布局是不是并不足以达到时序规范要求。我们为每个约束集运行100次构建,且在1-100次中采用不同的种子布局。

所用工具

对于FPGA设计软件,我们在设计人员的局部环境中采用赛灵思ISE®设计套件逻辑版本14.4来完成现有工作流程中的各项任务;在云端,我们用它来完成综合与布局布线任务。

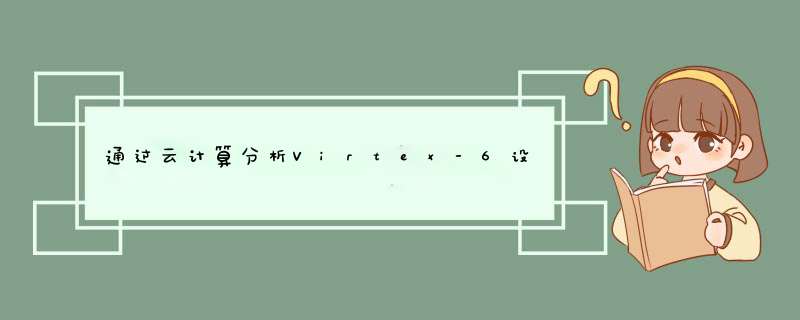

在前端,CSIR的Scineric Workspace(见图1)是一种用于FPGA设计管理的基于IP-XACT的全新、快速、轻量级集成开发环境。该工具采用全新“文件管理器”方法来进行设计管理,有助于设计人员随时全局预览设计的各个方面。它具有设计融合功能,可将Scineric整合到现有工作流程中,以提供用户偏好的特定设计环境。我们可使用载入ISE项目的Scineric Workspace图形界面向云端配置、提交并从云端检索构建。然而,这个前端并不是硬性要求;Plunify客户端还能平滑集成到ISE和Vivado®流程中。

在后端,Plunify的FPGA-Accel客户端是一种软件API,工程师们可通过它在远程服务器上同时定义、分配和执行FPGA综合以及布局布线构建,并在完成所有构建后对结果进行分析。本例中,我们采用一个云计算服务器群来处理400次构建。Scineric Workspace支持包括FPGAAccel客户端在内的多种配置。

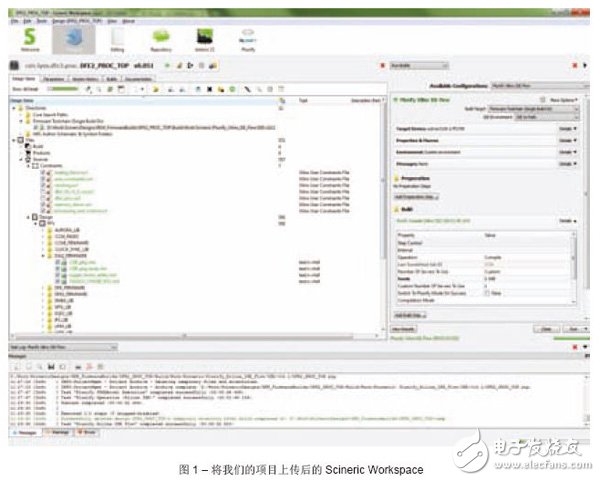

图2显示了设计人员在工作中如何使用这些工具。具体流程如下:

1. 打开Scineric Workspace。

2. 导入ISE项目。

3. 为每个ISE项目限定100次 实验。

Scineric Workspace允许用户导入赛灵思ISE和Vivado项目以及IP-XACT组件定义文件等各种来源的设计。每个设计都可以有多种构建配置,包括允许您对可随后上传至Plunify的Plunify实验进行定义的配置。

4. 上传构建请求。

Plunify插件首先会对设计人员的身份进行认证,然后再对ISE项目中的所有设计文件进行加密。接下来,它会将文件与构建参数一起安全传输至远程服务器群。

在云端,Plunify软件会生成所需的构建,分配400台服务器并运行ISE,从而在每台服务器上为各个不同的实验进行综合与布局布线。

5. 构建完成后,您会收到一封电 子邮件通知。

6. 用您的工作ID登陆至 www.plunify.com 查看报告

7. 对各个ISE项目重复以上步 骤。

并行完成400次构建

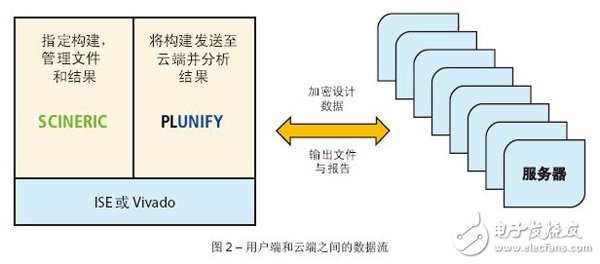

我们将这400次构建的结果用于多个标准测试,包括平均运行时间、不可布线的解决方案数量,以及可布线的解决方案的时序评分,这也是最重要的。图3显示了四个约束集的时序评分分析结果。

通过我们的四个约束集,我们得以再次证明,目标应用的无效管脚会严重影响设计的时序评分。另外,我们可为该设计确定最佳种子布局,并且在这个特定案例中,我们意识到实现工具在不受布局规划引导的情况下表现最佳。

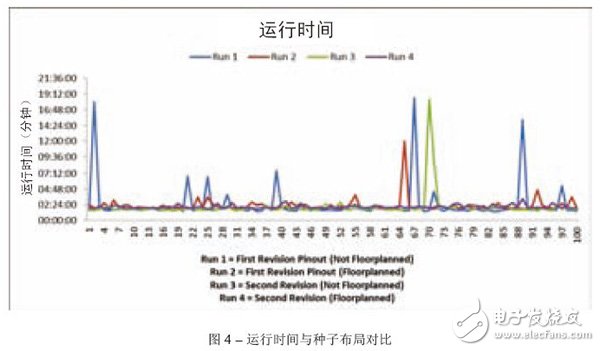

图4显示了四个约束集的运行时间。

以前,这样的运行需要30多天才能完成,但通过我们所说的方法,我们只需一天便能得到结果和分析。该方法的另一优势是全部数据都由Plunify管理,而这项优势是当我们看到这400次运行到底生成了多少数据时(200千兆字节)才发现到的。我们只需要下载自己感兴趣的特定运行结果。

最佳时序评分

在任何FPGA设计中,时序收敛都是重要的一环,我们已经证明,很多参数都会对您的时序评分产生影响。借助全新的工具以及云计算技术,我们对这些影响的分析速度与以往相比明显加快。

我们能够确定哪种约束集以及种子布局能为我们的设计带来最佳时序评分。通过使用最佳参数,我们可以继续下一阶段的系统开发,因为我们的构建能够达到其时序规范要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)