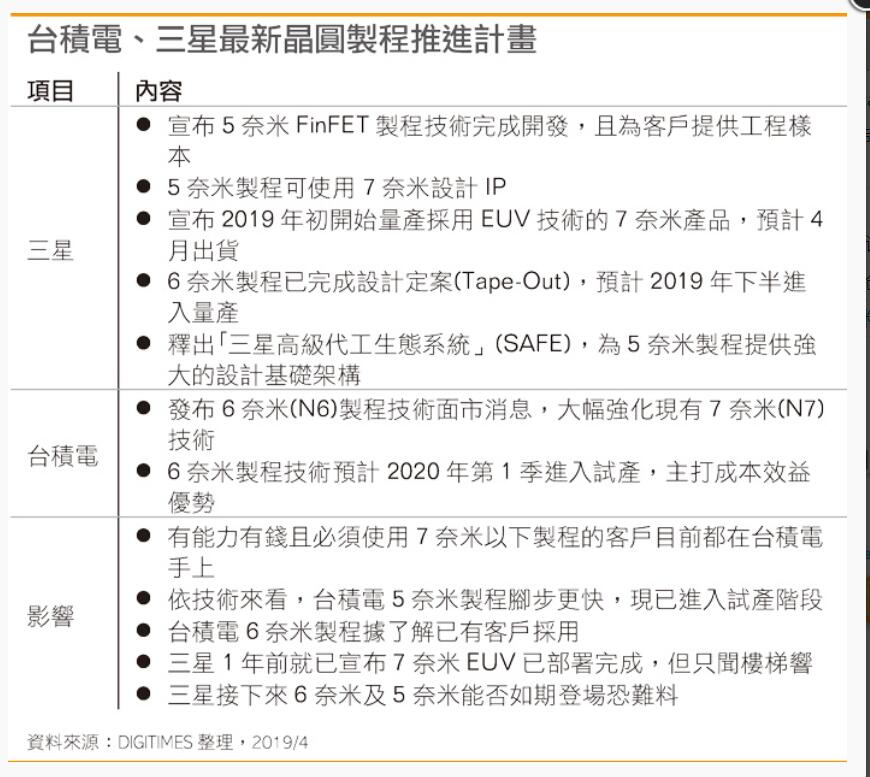

台积电4月16日晚宣布,推出6纳米(N6)制程技术,大幅强化7纳米(N7)技术。据其日前宣布5纳米已进入试产,台积电无疑越接近摩尔定律的极限。每隔一纳米,都要在7、6、5纳米制程一路通吃。值得注意的是,其主要竞争对手三星也在日前宣布完成5纳米EUV工艺研发,并已送样给客户,双雄竞争不相上下。

三星电子(Samsung Electronics)全面释出7、6、5纳米制程进度,台积电也罕见宣布从未曝光的6纳米制程技术计画。三星应暂不会对台积电有所威胁,但可能会再次形成客户挟转单三星威胁,要求台积电代工费降价情势。

三星电子16日大动作宣布最新制程推进计划,不仅已完成5纳米FinFET制程技术研发,首款6纳米芯片亦已完成设计定案(tape out)。

台积电表示,为了协助客户在效能与成本之间取得高度竞争力的优势,同时借由N7技术设计的直接转移而达到加速产品上市目标。借由目前试产中的7纳米强效版使用极紫外光(EUV)微影技术所获得的新能力,N6技术的逻辑密度较N7技术增加18%,同时,N6技术的设计法则则与N7完全相容,使得7纳米完备的设计生态系统能够被再使用。

台积电指出,N6技术预计于2020年第一季进入试产,提供客户更多具有成本效益的优势,并延续7纳米家族在功耗及效能上的领先地位,支援多样化的产品应用,包括高端到中端移动产品、消费性应用、人工智能、网通、5G基础架构、绘图芯片GPU以及高效能运算。

台积电业务开发副总精力张晓强指出,N6技术会比目前N7技术进一步延续领先地位,提供客户更高的效能与成本效益。

2019年台积电预计提供约1200万片12寸约当晶圆的年产能,全面覆盖大于0.5微米制程至最先进的7纳米工艺制程。

本文来自DigTImes, 本文作为转载分享。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)