对于使用安谋国际(ARM)处理器的系统单芯片(SoC)设计者而言,在原型制作的阶段经常会面临如何整合处理器的问题。本文以赛灵思(Xilinx)的Zynq为例,说明如何应用内嵌安谋国际核心的现场可编程门阵列(FPGA)做为安谋国际核心测试芯片,进而建构SoC原型制作平台。

验证SoC设计 FPGA原型最稳当FPGA原型制作是在FPGA上实作SoC或特定应用集成电路(ASIC)设计的方法,并进行硬件验证和早期软件开发。藉由这个接近真实ASIC的实作方式,设计人员可以用接近实时的速度,在真实的处理器上做软件测试与系统整合。

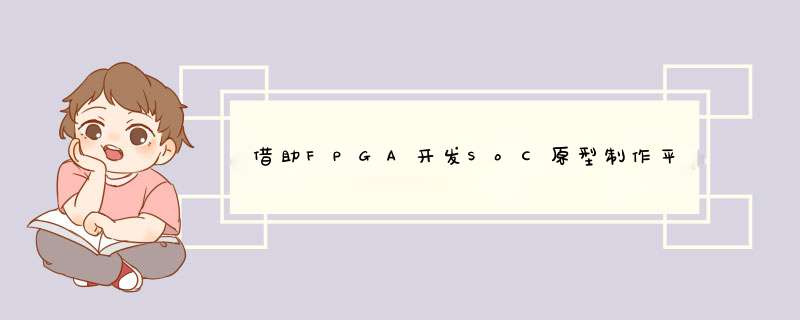

由于半导体制程的快速进步,每片芯片上可以放进的晶体管数目急遽增加,因此SoC的设计也变得更加庞大且复杂。芯片设计人员开始发现由于执行速度太慢和模型准确性的限制,光靠软件仿真来验证硬件设计是不够的。更严重的是,SoC的设计错误,常会隐藏在系统深处,只有在软硬件之间复杂的互动情形下,才会呈现出来,因此及早开始进行软件和韧体开发变得更加重要,而在这个阶段也只有FPGA原型的速度足以执行复杂的 *** 作系统和软件应用。总的来说,只有用FPGA原型来验证SoC设计才是最可靠的方法,且藉由FPGA原型才能做到软件和硬件的并行开发(图1)。

图1 SoC设计流程中的FPGA原型制作

借力测试芯片与核心板 SoC原型整合处理器迎刃解大多数的SoC设计都包含一个或多个处理器。随着所采用处理器的不同,其来源对原型制作的支持形式也迥异,可能是用来刻录在FPGA里的缓存器转化层(RTL)程序或已经编译和优化的比特流(Bitstream),也可能是电路板上面载有处理器芯片或已刻录线路的FPGA。

对于使用安谋国际处理器的SoC设计者而言,在原型制作的阶段常会面临如何整合处理器的问题。一般的解决方式如下:

测试芯片测试芯片(Test Chip)是安谋国际和合作厂商为了验证新的处理器设计和制程所制作的芯片,因此测试芯片中包含安谋国际处理器硅智财(SIP),以及一些必需的逻辑线路,如控制频率用的锁相回路(PLL)和频率分频器(Clock Divider),及边界扫描(Boundary Scan)测试线路等。测试芯片常会对内嵌处理器的接口讯号做处理,以减少所需的接脚数目,从而降低封装成本,如把多个先进微控制器总线架构(AMBA)接口用多任务方式(MulTIplexed)变成一组外接讯号。

测试芯片和一般内嵌安谋国际处理器的SoC最大不同之处,即在于它提供直接从处理器AMBA界面拉出来的接脚,因此使用测试芯片便可以把兼容于AMBA界面的周边设计接上处理器,从而形成完整的应用系统。

测试芯片内的安谋国际处理器可以提供接近ASIC的执行速度,不过测试芯片制作成本甚高,一般很难取得。

核心板

一般开发者只能以核心板(Core TIle)的型式取得具有AMBA外接接口的安谋国际处理器芯片。

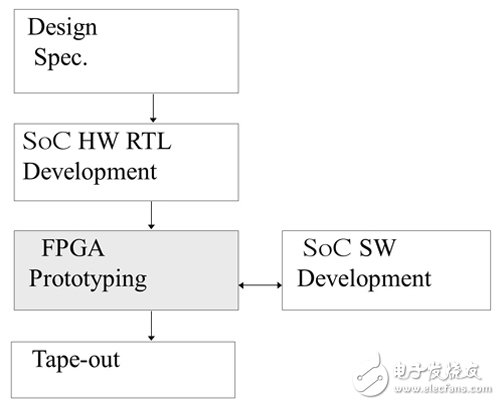

核心板是上面载有测试芯片的子板,且板上的连接器提供测试芯片的AMBA接口讯号。核心板是安谋国际开发平台的一部分,须装在基板(Baseboard)上使用,由基板提供电源、内存及周边,若是要扩充FPGA可以再加上可程序逻辑板(Logic TIle);这些开发板合起来构成完整的原型系统,让开发者用来评估处理器、进行效能测试、开发软件或验证IP设计(图2)。开发者可以购买到这些开发板,不过价钱并不便宜。

图2 ARM开发平台

另有部分市售的FPGA原型制作平台亦使用核心板加入安谋国际处理器,这些平台的共同点为提供FPGA和核心板之间的连接方式,如透过另一子板及其上的高速连接器,以转接核心板到原型制作平台上。

由于核心板上测试芯片接口讯号的接脚众多,若设计者欲把核心板连接到自制的FPGA原型制作平台上,在设计时就要考虑到接口和连接的问题。

对于使用安谋国际(ARM)处理器的系统单芯片(SoC)设计者而言,在原型制作的阶段经常会面临如何整合处理器的问题。本文以赛灵思(Xilinx)的Zynq为例,说明如何应用内嵌安谋国际核心的现场可编程门阵列(FPGA)做为安谋国际核心测试芯片,进而建构SoC原型制作平台。

内嵌ARM核心的FPGA倾巢出SoC FPGA并不是新产品,这类结合硬式核心(Hard-core)处理系统和可程序逻辑的产品,早就用在除了处理器和周边之外,另须外加逻辑的应用中。它的可程序逻辑可用来进行大量运算或讯号处理,以提升系统整体效能;此外,这类产品亦可做为许多应用的单芯片解决方案。

过去这类产品的硬式核心处理器多采用PowerPC核心,不过随着安谋国际核心的普及,目前已有三家厂商推出内嵌安谋国际核心的FPGA,其中美高森美(Microsemi)的SmartFusion内嵌应用广泛的Cortex-M3硬式核心微控制器(MCU),而Altera的Cyclone V和Arria V系列,以及赛灵思的Zynq-7000系列都选择内嵌更高效能的双核心Cortex-A9处理器。

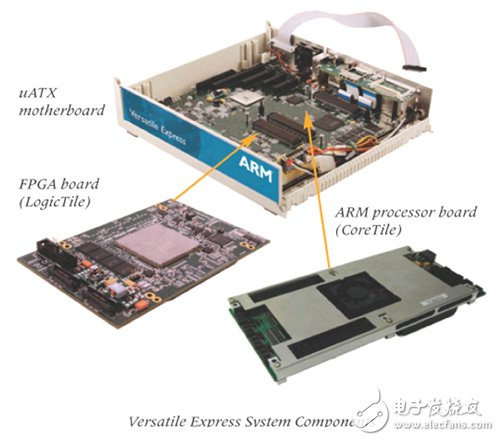

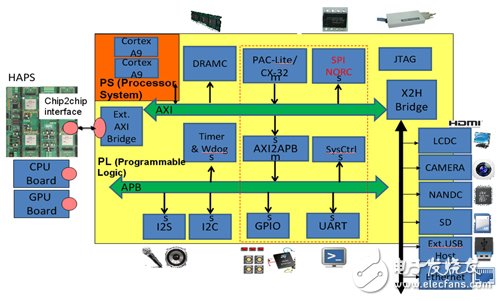

借助Zynq开发SoC原型实作Zynq包含处理系统(Processing System, PS)和可程序逻辑(Programmable Logic, PL)两部分(图3)。

图3 Zynq FPGA功能方块图

PS处理系统是如同ASIC一般的固定硬件(Hard-wired),相当于一个内嵌于FPGA中既定架构的安谋国际处理系统,其包含双核心、频率可达800MHz的Cortex-A9处理器,及固定硬件的双倍数据率(DDR)和闪存控制器;此外,固定硬件的部分还包含以太网络(Ethernet)、第二代通用串行总线(USB)2.0、控制器局域网络(CAN)、安全数字输入/输出(SDIO)、内部整合电路(I2C)、串行周边接口(SPI)、通用异步收发器(UART)和通用输入/输出(GPIO)等常见的嵌入式系统周边。

Zynq-7000系列产品都内嵌一样的安谋国际处理系统,但是PL可程序逻辑的大小则各有不同。两个较大的产品容量分别相当于一百九十万和三百五十万个ASIC逻辑闸,而两个较小的产品容量分别相当于四十三万和一百三十万个ASIC逻辑闸。

连接PS和PL的是AXI接口。安谋国际所制定的AMBA接口是SoC On-chip Bus的实际标准,它已为满足芯片容量增加随之而来的效能需求修订好几版,最新的规格就是AXI(Advanced eXtensible Interface)。

由此可知,Zynq FPGA即包含处理器核心和可程序逻辑,且使用和ASIC同样的AXI接口连接,很明显地它可以用作SoC原型制作,因此使用Zynq即能建构一个支持Cortex-A9设计的原型制作平台。

AXI接口评估要点Zynq连接PS和PL的AXI接口有好几种,各有不同的特性,因此当你决定要用Zynq做为原型制作平台时,马上就面临一个问题:在这几种AXI接口之中,究竟要用哪个来做为处理器和SoC其他部分连接的原型?PL中的逻辑要跟哪个AXI接口连接才能接到处理器,而不只是接到处理系统的内存控制器和周边?

连接PS和PL的有三种AXI接口:通用(General-purpose)、高效能(High-performance)和加速一致性端口(Accelerator Coherency Port, ACP)。对PS而言,有两个到PL的通用Master AXI接口和两个从PL来的通用Slave AXI接口。Master在这里指的是数据传输的发起者,而Slave只能响应数据传输的要求。PS的Master AXI接口一般是用来对PL中的周边做传输,而Slave AXI接口则用来响应PL的要求。此外,还有四个高效能(64位宽度)的AXI接口,这四个接口对PS来说都是Slave,且都接到PS里的内存控制器,用来让PL里的Master存取内存。最后,ACP则是另一个从PL到PS的32位Slave AXI接口。

因此,若要用安谋国际处理器做为Master连接PL,必须用那两个通用Master AXI接口。这两个接口均相同,因此使用任一个皆可。

具功能扩充性 Zynq FPGA巧扮SoC原型平台对不具备印刷电路板(PCB)设计能力的公司而言,使用市售的FPGA原型制作平台是最省时且有效的方法,但若使用这些平台亦会受到既定系统配置与架构限制,无法自由发展满足需求的系统架构,且在传输带宽和执行频率方面也缺乏d性。相反地,自行制作平台就很容易满足设计人员的需求,如可以在板上使用某些特定的周边和组件等。

成本也是选择自行制作平台的一个考虑因素。为发配给每位团队成员平行开发软件,因此需要有多片平台,使得自行制作所需的成本相较于购买市售平台来得低廉。

为实现自主架构SoC的原型制作,Zynq FPGA包含DDR、储存型快闪(NAND Flash)和SPI Serial Flash等内存控制器,以及互补式金属氧化物半导体影像传感器(CMOS Image Sensor)、液晶显示器(LCD)、高分辨率多媒体接口(HDMI)、SD Card、USB Host、以太网络、音频编译码(Audio CODEC)、UART、GPIO和JTAG(Joint Test AcTIon Group)等周边界面(图4)。

图4 Zynq FPGA 原型制作平台

至于PS内的固定硬件周边,虽然在验证个别IP时可以加以应用,但是它们还需要在板上有所属的特定线路和组件才能使用,如此会大幅增加电路板布局的复杂度,因此只好放弃不用;不过若选择使用固定硬件的DDR控制器,就可以在验证工作一开始时,就有可以运作的DDR内存功能。

此外,在板上还配置了扩充用连接器。用户只要设计可以接到此连接器的电路板,即可扩充平台的功能,这是扩充平台功能最快也最省钱的方法;此外,它也可以用在连接其他FPGA板以扩充容量和周边,或是用于对架构的探索研究。

利用Zynq FPGA还可以实现「测试芯片模式(Test Chip Mode)」,也就是只使用Zynq做为安谋国际测试芯片,用来支持其他FPGA板的原型制作。实现「测试芯片模式」时,设计人员只须把Zynq内处理器的AXI接口讯号经过PL拉到外部接脚上即可。

当要把AXI接口讯号拉到Zynq外部接脚时,若可用的接脚数目不够,就要使用接脚多任务(Pin Multiplexing)或某些桥接(Bridging)的方法来减少使用接脚数目;以我们设计的桥接方式为例,用32位数据宽度做传输时所需的接脚数目为四十四(包括控制讯号);而用16位数据宽度做传输时所需的接脚数目为二十八。不过因为这些方法都是用牺牲传输带宽的方式换取使用较少的接脚数目,因此会造成效能的下降。

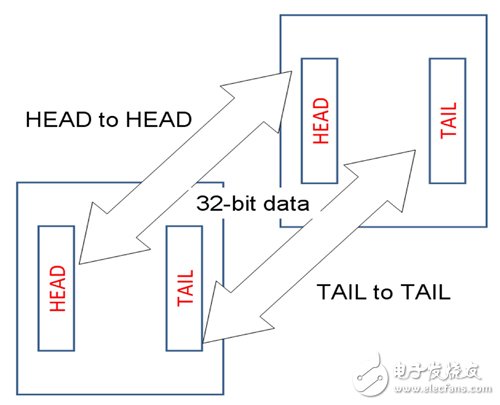

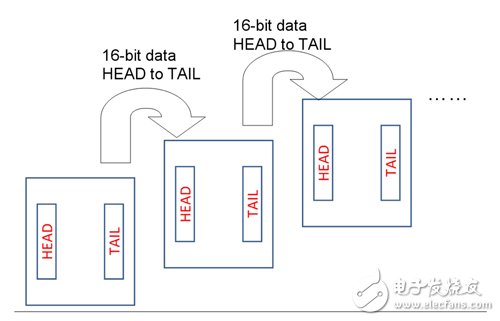

针对用多片相同的Zynq FPGA板来做扩充的需求,板上的扩充用连接器也有特殊的配置:在板的左右两侧各配置有四十接脚的连接器,扣除电源接脚后每个连接器可用的接脚数目为二十八,正是前述桥接方式用16位数据宽度做传输时所需的接脚数目,如此使用多片Zynq FPGA板做板对板连接,即可分别支持32位数据宽度的双板对接模式(图5)和16位数据宽度的多板串接模式(图6)。

图5 Zynq FPGA板的板对板连接(32位数据宽度的双板对接模式)

图6 Zynq FPGA板的板对板连接(16位数据宽度的多板串接模式)

打造SoC原型制作平台 FPGA SoC崭露头角SoC的原型制作已是达成硬件验证和及早进行软件和韧体开发的主流方法。相较于找寻合适的处理器核心测试芯片或使用既定架构的安谋国际原厂开发板,利用内嵌安谋国际核心的FPGA即可轻松实现SoC的原型制作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)