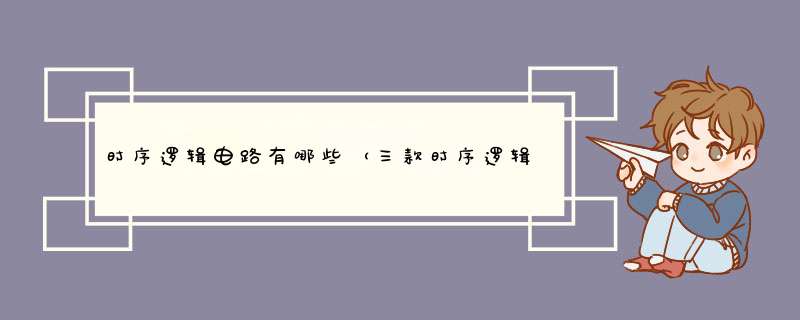

在数字电路中,凡是任一时刻的稳定输出不仅决定于该时刻的输入,而且还和电路原来状态有关者都叫时序逻辑电路。时序逻辑电路结构示意图如图2-41所示。时序逻辑电路的状态是靠具有存储功能的触发器所组成的存储电路来记忆和表征的。

1、功能特点

电路在某采样周期内的稳态输出Y(n),不仅取决于该采样周期内的“即刻输入X(n)”,而且还与电路原来的状态Q(n)有关。(通常Q(n)记录了以前若干周期内的输入情况)。

2、结构特点

除含有组合电路外,时序电路必须含有存储信息的有记忆能力的电路:触发器、寄存器、计数器等。

时序逻辑电路的功能1、逻辑方程组

1)特性方程:描述触发器逻辑功能的逻辑表达式。

2)驱动方程:(激励方程)触发器输入信号的逻辑表达式。

3)时钟方程:控制时钟CLK的逻辑表达式。

4)状态方程:(次态方程)次态输出的逻辑表达式。

5)输出方程:输出变量的逻辑表达式。

2、状态表

反映输出Z、次态Q*与输入X、现态Q之间关系的表格。

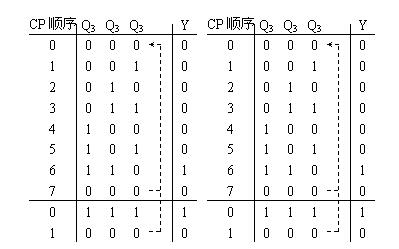

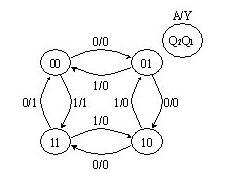

3、状态图

反映时序电路状态转换规律及相应输入、输出取值关系的图形。

4、 时序图

又叫工作波形图,它用波形的形式形象地表达了输入信号、输出信号、电路的状态等的取值在时间上的对应关系。

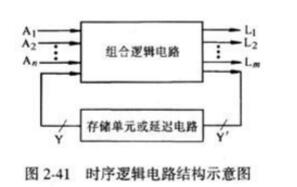

时序逻辑电路的状态转换表、状态转换图和时序图详解状态转换表、状态转换图和时序图是时序电路特有的描述方法,描述出电路在 CP 作 用下,状态转换全部 过程。

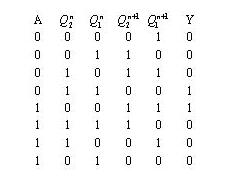

一、状态转换表

将输入及初态代入状态方程和输出方程,算出电路次态和现态下的输 出值。

即:每 7 个 CP ,电路状态回到初态(循环变化)。可对时钟脉冲计数:每经过 7 个时钟脉冲, Y 输出一个脉冲(即由 0 变 1 ,再由 1 变 0 ),可作为一个 七进制计数器, Y 输出进位脉冲。

二、状态转换图

三、时序图(即: CP 作用下,电路状态、输出状态随时间变化的波形图)

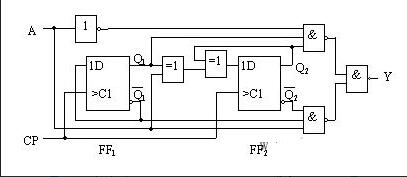

P231 例

解: ( 1 ) 写出 驱动方程: ![]()

![]()

( 2 ) 由 D 触发器特性方程: ![]() 得 状态方程:

得 状态方程:

![]()

![]()

![]()

![]()

( 3 )输出方程: ![]()

( 4 )状态转换表:

( 5 )状态转换图:

( 6 )逻辑功能: A=0 ,为 4 进制加法计数器, ![]()

![]() 由 00 、 01 、 10 、 11 递增,从 11 跳变回 00 时,输出端 Y 输出一个脉冲。A=1 ,为 4 进制减法计数器,

由 00 、 01 、 10 、 11 递增,从 11 跳变回 00 时,输出端 Y 输出一个脉冲。A=1 ,为 4 进制减法计数器, ![]()

![]() 由 11 、 10 、 01 、 00 递减,从 00 跳变回 11 时,输出端 Y 输出一个脉冲。

由 11 、 10 、 01 、 00 递减,从 00 跳变回 11 时,输出端 Y 输出一个脉冲。

时序逻辑电路的设计(一)

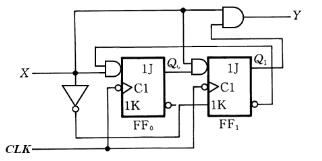

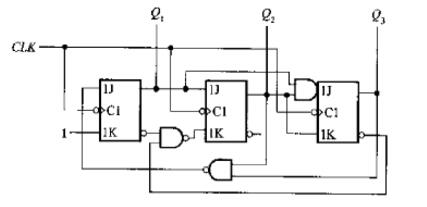

下图的时序逻辑电路是:设计一个串行数据检测器,对它的要求是:连续输入3个或3个以上的1时输出为1,其他输入情况下输出为0。

时序逻辑电路的设计(二)

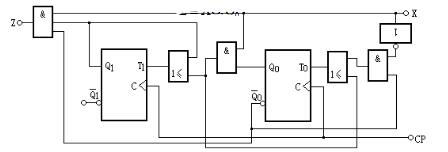

下图的时序逻辑电路是:试用JK触发器和门电路设计一个同步七进制计数器

时序逻辑电路的设计(三)

下图的时序逻辑电路是:设计一“011”序列检测器,每当输入011码时,对应最后一个1,电路输出为1

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)