前言

为了提高现代无线设备的灵敏度和可选择性,需要尽可能地减小相位噪声和参考杂散,并缩短锁定时间。本文中所述电路可以改善本振(LO)的所有这些性能。

相位噪声是对LO信号的纯度的一种量度。相位噪声是载波功率相对于给定的频率偏移处(频率合成器通常定义1kHz 频率偏移)1-Hz的带宽上的功率。其计算结果以dBc/Hz为单位表示。

由于频率合成器内部的开关切换,输出信号中会出现杂散(spurs)。在整数N分频的合成器中,它们一般是由于鉴相器(PFD)的工作频率点上的信号分量所引起的;在小数N分频中,它们是由合成器本身架构的特点所造成的。在整数N分频锁相环(PLL)中,它们被称为参考杂散(reference spurs)。

锁定时间是指输出从一个频率切换到另一个频率所需要花费的时间——这对于许多系统来说是一个重要的指标。一般说来,当输出稳定到所期望的最终频率附近、差异在某一百分比[或者以百万分之一(ppm)衡量]之内,或是相位锁定在所需要相位度数的附近,此时我们说,输出被切换到或者锁定到新的频率上了。

传统的接收机实现方式

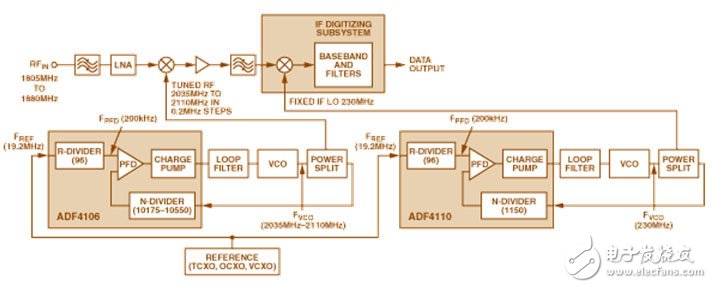

图1所示的是最通用的的接收机架构的功能框图(超外差接收机)。这里所示出的系统是满足DCS1800移动电话标准接收机的典型结构。在该标准中,接收(Rx)频段是1805MHz~1880MHz。

图1中,RF输入信号先流经一个RF滤波器,接下来再经过一个低噪声放大器(LNA)。随后,信号在混频器中与一个可调谐的LO输入进行混频,变换到中频段(IF)。混频后的信号接受进一步的滤波,在通过一个最终的混频器,与一个固定频率的LO信号混频,从固定的IF频段下变频到基带信号频段上。

可调谐的RF LO信号是利用一路干净和稳定的参考频率信号来生成的,该基准信号输入至ADF4106 PLL合成器和一个压控振荡器(VCO)中后最终形成LO信号。参考频率信号可以由温补晶振(TCXO)、压控晶体振荡器(VCXO)或者恒温晶体振荡器(OCXO)来产生。 在整数N分频系统中,PLL合成器的R分频器将该参考信号变换成为一个频率等于信道间隔的信号——或者,在小数N分频系统中,将信号频率变换成信道间隔的倍数。PFD则对环路输出FVCO除以N后的结果与R分频器的输出进行比较,然后,环路驱动VCO,使得FVCO = FPFD &TImes; N,以使PFD输出归零。可以通过改变N来改变LO输出频率,从而对无线电路进行调谐。

LO的相位噪声取决于多方面的因素:参考信号噪声、合成器中的噪声(R分频、N分频、PFD和电荷泵),N值,以及PFD的工作频率。

LO的相位噪声(dB)可以用如下的公式来表示:

式中

PNSYNTH是合成器对相位噪声的贡献(在数据手册中给出,单位是dB)

20 logN是合成器中的N值所带来的附加噪声

10 logFPFD是合成器的PFD频率所产生的噪声分量

*欲获得更多详情,请参阅“Design a Direct 6-GHz Local Oscillator with a New, Wideband, Integer-N, PLL Synthesizer”(Analog Dialogue, Volume 35, No. 6, November-December, 2001)

参考杂散取决于如下因素:PFD设计,PFD电路中电荷泵的漏电,PLL环路带宽,VCO灵敏度。锁定时间取决于PFD频率和PLL环路带宽。

在接收机中, 如果IF选定为230MHz,经过调谐的RF信号将在2035~2110MHz范围内变化(使用高端注入),步进为200kHz。如果使用整数N分频架构来实现的话,则需要使用200kHz的PFD频率,而N值将从10175(2035MHz)变化为10550(2110MHz)。

在商业应用系统中所期望的带内相位噪声为-85.6 dBc/Hz,采用适合的锁相环,如ADF4106,系统的典型基准寄生为-88dBc @ 200kHz和-90dBc @ 400kHz。

图1 传统的超外差接收机的系统框图

如果环路带宽选取为20kHz,则相位差小于10度时对应典型的锁定时间将为250µs。

接收机的另一种可替代方案

ADI公司目前提供一种新的宽带宽PLL合成器——ADF4107。其RF级可以在高达7.0GHz的频率下工作,而PFD频率可以高达104MHz。这样的宽带宽工作能力可以用于实现新颖的接收机架构,如图2所示。在该结构中,每一级的LO都可以从一路频率为所需频率的整数倍的信号变换得到。此外,调谐是在IF部分完成的。这就容许系统采用非常高的倍率,以便改善总的相噪声和锁定时间性能。

固定频率的RF电路

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)