在集成度高度发展的今天,不能靠多个晶振源来解决问题,而且一旦晶振固定那么它的灵活性和可移植性必然受到很大影响,所以一些时钟分频芯片应运而生,今天我们将举一个很有代表性的AD9522时钟分频芯片的典型应用来达到一个抛砖引玉的作用。

一、AD9522简介1.外部特性

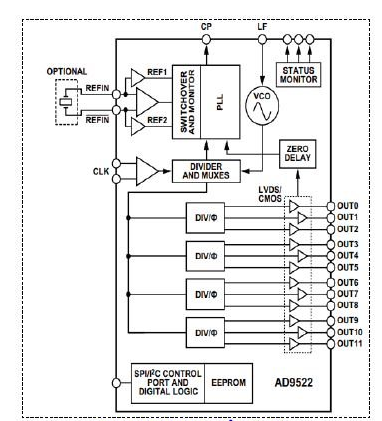

A D 9 5 2 2是一个多路时钟输出和分配功能的芯片,本身支持亚皮秒抖动性能,在芯片内部还集成了PLL(PhaseLockedLoop)和VCO(压控振荡器)。VCO的调谐范围是 2.02GHz~2.335 GHz.AD9522串行接口支持SPI与I2C的数据总线,芯片内部的EEPROM可通过串口进行编程,可以用来存储用户配置的寄存器数据从而使输入时钟分频。AD9522具有12路的LVDS电平输出,可以分成4组,每组输出都有分频器,分频比1-32之间可以在其范围内随意设置。如图1所示。

2.内部特性

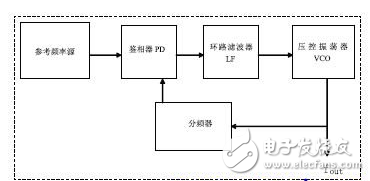

AD9522外部的输入时钟是晶振供给的,内部时钟的倍频和分频都是由锁相环PLL和压控振荡器VCO控制的。例如压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL的电压输出端的电压发生变化,去控制VCO,直到相位差恢复,达到锁频的目的。如图2.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)