随着可综合模拟电路设计的出现,数字电路性能越来越强,模拟电路却由于电源电压的下降而导致设计更加困难。有时候但你学习电路的时候你会傻傻的分不清模拟电路和数字电路。

1.模拟与数字合体,结果是?模拟电路和数字电路是对电路的经典分类。数字电路处理离散的数字信号,模拟电路处理连续的模拟信号。在经典的课本里,模拟电路和数字电路设计与分析的方法论都有很大区别,模拟电路的分析像物理,设计则像一门艺术;数字电路的分析像数学,而设计起来是一板一眼,基于严密的逻辑流程。

然而,模拟和数字之间的间隔并非不可打破。一方面,信号的本质是连续的,一切数字电路只是模拟电路的一种特例,甚至可以把数字电路用在模拟电路中(例如反相器也可以当作一个放大器用,而且是电流复用的那种J);另一方面,利用数字电路可扩展性好,可控性好等特性,我们可以把一些传统在模拟域处理的信号搬到数字域处理并获得很好的结果。模拟和数字合体的结果并不仅仅是混合信号电路,而是一种全新的设计理念。

模拟和数字融合可以分成两种方向,即使用数字方法实现传统的模拟电路(数字-模拟),以及使用模拟方法实现传统的数字电路(模拟-数字)。本期我们主要介绍数字-模拟电路。

2.数字-模拟随着半导体技术的发展,越来越多人正在探索把原来模拟域处理的信号搬到数字域处理。这不仅仅是标新立异,而且是由半导体技术发展的趋势决定的。所以啊,一个电路的命运不知要看工程师的奋斗,还要看历史进程。

那么,半导体技术如何让数字技术入侵模拟电路呢?大家都知道,随着半导体制程的发展,器件特征尺寸变小,器件速度变快,这对于数字电路和模拟电路都是件好事,皆大欢喜。然而,特征尺寸变小是要付出相应代价的。代价第一就是随着MOSFET栅极氧化层变薄,器件击穿电压降低,因此电源电压也随之降低。这对于数字电路来说对性能影响会被栅电容变小期间速度变快而抵消因此不是太大的问题,但对于模拟电路来说问题可就大了。首先,模拟电路的首要指标是信噪比,降低电压意味着信号摆幅降低,但是噪声不会与电源电压同步降低,因此低电压对于信噪比存在不利影响。其次,器件的阈值电压因为漏电的关系也不会与电源电压同步降低,这就让传统cascode等模拟工程师喜闻乐见的电路结构在低电压下无法再使用。最后,因为阈值电压与电源电压没有同步降低,因此在低电源电压下器件的工作范围更接近于亚阈值区,因此模拟电路的线性度变差了

除了电源电压降低带来的诸多问题以外,先进半导体制程的单位面积价格很高,但是模拟电路的整体尺寸并不随着特征尺寸缩小而等比例缩小(尤其是无源器件例如电感,其大小与特征尺寸根本就没关系),因此在先进半导体制程下模拟电路的成本其实是升高了。

与模拟电路相反,特征尺寸缩小对于数字电路性能有益无害(除了漏电流增加,但是这个可以说不算性能:)),因此用数字电路尽量代替模拟电路才能真正享受半导体工艺进化带来的益处。

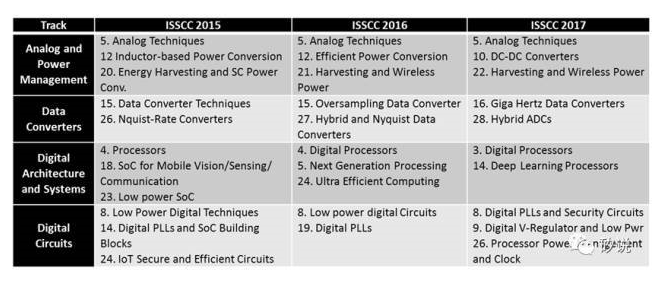

从近三年年ISSCC的track比较也能看出数字慢慢进入模拟领域代替经典模拟电路的趋势。在ISSCC 10个大track中,模拟track包括传统模拟电路与功耗管理(Analog),模数转换器(Data Converters)。数字track包括架构与系统(Digital Arch and Sys),和数字电路(Digital Circuits)。 然而,在下面的列表中,也有“Digital PLL”,“Digital V-Regulator and Low Pwr”这样有趣的session。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)