锁相环(PLL)是一种反馈系统,其中电压控制振荡器(VCO)和相位比较器相互连接,使得振荡器可以相对于参考信号维持恒定的相位角度。在使用PLL的过程中您都遇到过哪些问题呢?咱们工程师整理了PLL芯片接口方面最常见的11个问题,这里分享给大家!

1、参考晶振有哪些要求?该如何选择参考源?

波形: 可以使正弦波,也可以为方波。

功率: 满足参考输入灵敏度的要求。

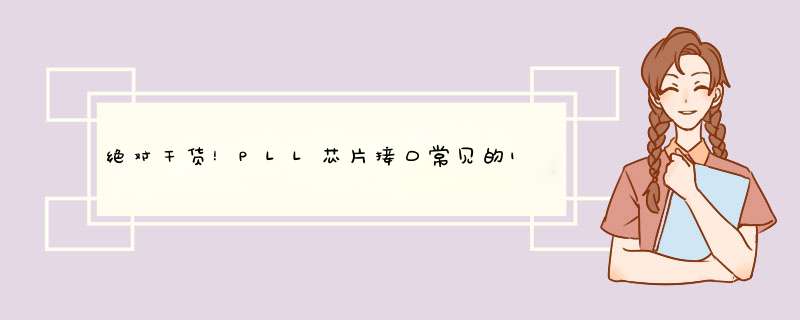

稳定性: 通常用TCXO,稳定性要求< 2 ppm。这里给出几种参考的稳定性指标和相位噪声指标。

频率范围:ADI 提供的PLL 产品也可以工作在低于最小的参考输入频率下,条件是输入信号的转换速率要满足给定的要求。

建议

在PLL 频率综合器的设计中,我们推荐使用温度补偿型晶振(TCXO)。在需要微调参考的情况下使用VCXO,需要注意VCXO 灵敏度比较小,比如100Hz/V,所以设计环路滤波器的带宽不能很大(比如200Hz),否则构成滤波器的电容将会很大,而电阻会很小。普通有源晶振,由于其温度稳定性差,在高精度的频率设计中不推荐使用。

2、能详细解释下控制时序、电平及要求吗?

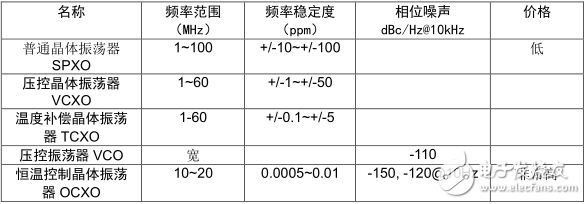

ADI 的所有锁相环产品控制接口均为三线串行控制接口,如图1所示。要注意的是:在ADI 的PLL 产品中,大多数的时序图如图1中上面的图所示,该图是错误的,正确的时序图如图1中下面的图所示,LE 的上升沿应跟Clock 的上升沿对齐,而非Clock 的下降沿。

图1、PLL 频率合成器的串行控制接口(3 Wire Serial Interface)

控制接口由时钟CLOCK,数据DATA,加载使能LE 构成。加载使能LE 的下降沿提供起始串行数据的同步。串行数据先移位到PLL 频率合成器的移位寄存器中,然后在LE 的上升沿更新内部相应寄存器。注意到时序图中有两种LE 的控制方法。

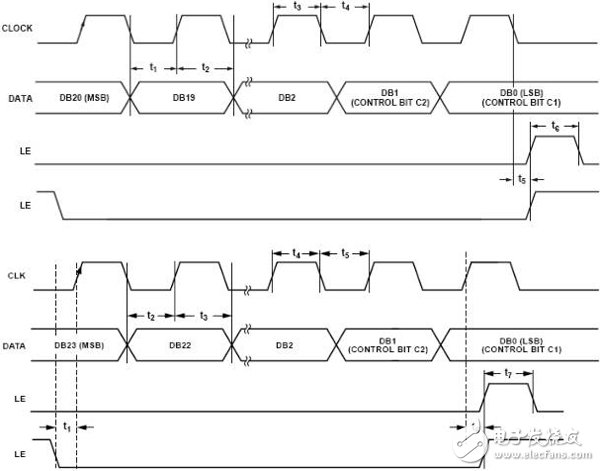

SPI 控制接口为3V/3.3V CMOS 电平。另外,需要注意的是对PLL 芯片的寄存器进行写 *** 作时,需要按照一定的次序来写,具体请参照芯片资料中的描述。特别地,在对ADF4360 的寄存器进行 *** 作时,注意在写控制寄存器和N计数器间要有一定的延时。

控制信号的产生,可以用MCU,DSP,或者FPGA。产生的时钟和数据一定要干净,过冲小。当用FPGA 产生时,要避免竞争和冒险现象,防止产生毛刺。如果毛刺无法避免,可以在数据线和时钟线上并联一个10~47pF 的电容,来吸收这些毛刺。

3、控制多片PLL 芯片时,串行控制线是否可以复用?

一般地,控制PLL 的信号包括:CE,LE,CLK,DATA。CLK 和DATA 信号可以共用,即占用2 个MCU 的IO 口,用LE 信号来控制对哪个PLL 芯片进行 *** 作。多个LE 信号也可以共用一个MCU 的IO 口,这时需要用CE 信号对芯片进行上电和下电的控制。

4、可否简要介绍环路滤波器参数的设置?

ADIsimPLL V3.3 使应用工程师从繁杂的数学计算中解脱出来。我们只要输入设置环路滤波器的几个关键参数,ADIsimPLL 就可以自动计算出我们所需要的滤波器元器件的数值。这些参数包括,鉴相频率PFD,电荷泵电流Icp,环路带宽BW,相位裕度,VCO 控制灵敏度Kv,滤波器的形式(有源还是无源,阶数)。计算出的结果往往不是我们在市面上能够买到的元器件数值,只要选择一个最接近元器件的就可以。

· 通常环路的带宽设置为鉴相频率的1/10 或者1/20。· 相位裕度设置为45 度。

· 滤波器优先选择无源滤波器。

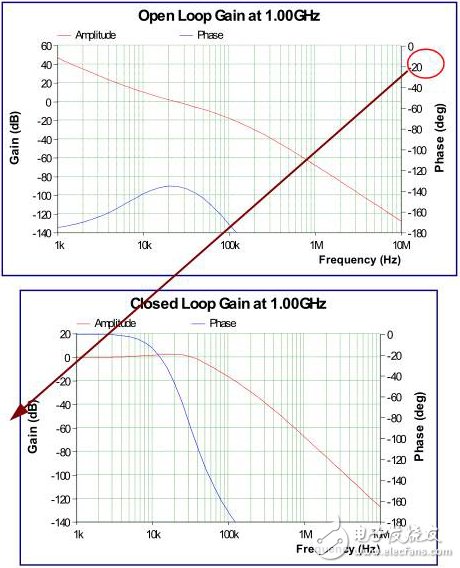

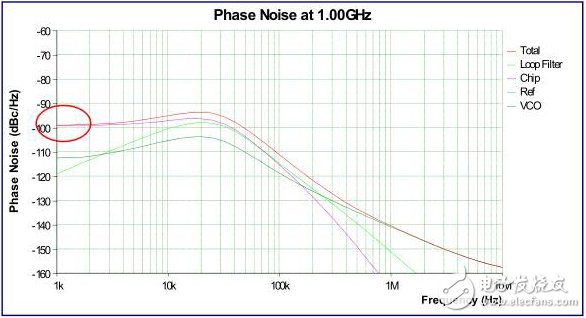

滤波器开环增益和闭环增益以及相位噪声图之间的关系。闭环增益的转折频率就是环路带宽。相位噪声图上,该点对应于相位噪声曲线的转折频率。如果设计的锁相环噪声太大,就会出现频谱分析仪上看到的转折频率大于所设定的环路带宽。

5、环路滤波器采用有源滤波器还是无源滤波器?

有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的PLL 产生的频率的相位噪声性能会比采用无源滤波器的PLL 输出差。因此在设计中我们尽量选用无源滤波器。其中三阶无源滤波器是最常用的一种结构。PLL 频率合成器的电荷泵电压Vp 一般取5V 或者稍高,电荷泵电流通过环路滤波器积分后的最大控制电压低于Vp 或者接近Vp。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)