在日常数字逻辑电路实验中编码译码显示实验电路是编码、译码、显示三个电路的综合运用, 在数字逻辑实验电路中具有重要的地位, 在实验的过程中, 时常会出现显示结果的抖动, 经研究出现这种现象主要原因是:编码电路的编码信号输入采用手工拨盘方式, 产生的编码输入信号往往不稳定; 另外, 电路控制性能较差,不能达到自动复位, 为此有必要对现有电路进行改进,在电路的设计上采用89C51 单片机为控制电路制作而成, 自动提供稳定编码输入信号, 显示结果稳定性和电路控制性能大大提升, 提高了教学实验质量。

1 编码译码显示实验电路的基本结构编码译码显示电路的基本结构如图1 所示, 主要由控制电路、编码信号发生器、编码译码显示电路等组成,控制电路产生编码信号作为编码译码显示电路输入信号, 译码电路将编码信号转换成对应的七段数码显示信号, 送至LED 数码管显示。

图1 编码译码显示实验结构图。

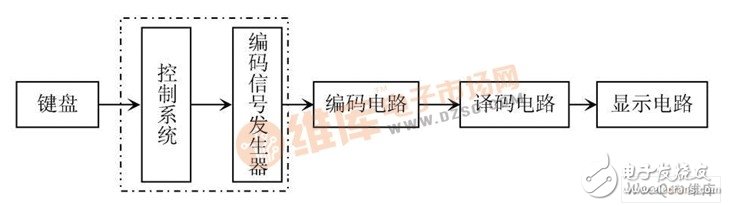

2 系统硬件设计控制系统和编码信号发生器采用89C51 单片机实现。89C51 性价比较高, 采用12 MHz 晶振, 其内部带有4 KB 的FLASH ROM, 无须外扩程序存储器。编码译码电路没有大量运算和暂存数据。89C51 内部的128 B片内RAM 已能满足要求, 无须外扩片外RAM。

系统硬件设计如图2 所示。

图2 编码译码显示实验电路。

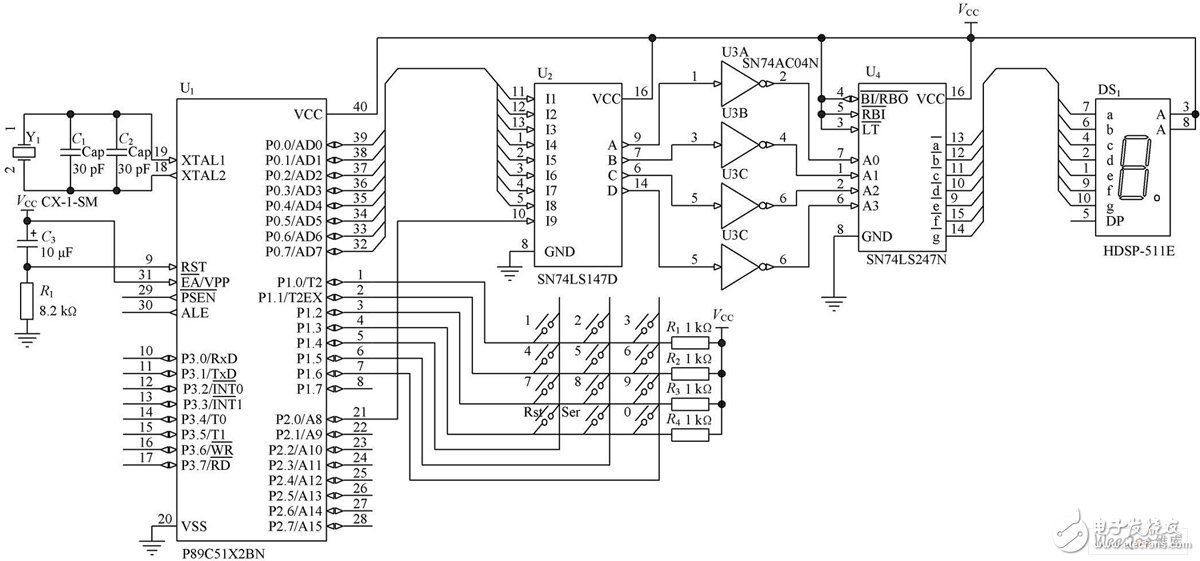

2. 1 编码信号发生器电路编码信号由89C51 内部编程控制, 键盘输入 0~ 8从P0. 0~ P0. 7 口送给编码器74LS147, 9 从P2. 0 口送给编码器, 具体编码见表1。

表1 编码信号表

键盘采用4×3 阵列结构设计, P1. 0~ P1. 3 为键盘扫描高4 位, P1. 4~ P1. 6 为低4 位。设计有 0 ~ 9 、Rst( 复位) 、S er( 顺序) 。列线通过电阻接正电源, 并将行线所接的单片机的I/ O 口作为输出端, 而列线所接的I/ O 口则作为输入。当按键没有按下时, 所有的输出端都是高电平, 代表无键按下。行线输出是低电平,一旦有键按下, 则输入线就会被拉低, 这样, 通过读入输入线的状态就可得知是否有键按下。

2. 3 编码译码显示电路编码译码显示电路主要由编码器( 74LS147) 、六反相器( 74AC04) 、译码器( 74LS247) 、七段LED 数码管组成。编码器74LS147 的1~ 5 脚, 10~ 13 脚为编码输入端, 低电平有效, 实验时可用接地作为低电平输入;14, 6, 7, 9 脚为编码输出( 反码) ; 16, 8 脚为电源正负极。

译码器74LS247 的6, 2, 1, 7 脚为译码输入( 高电平有效) ; 9~ 15 为译码输出; 8, 16 脚为电源正负极。六反相器( 74AC04) 主要是解决编码器74HC147 和译码器74LS247 信号匹配问题, 共有6 组输入与输出, 只取其中4 组。七段LED 数码管主要是显示译码器输出状态。

电路主要原理是在74LS147 的  输入011111111~ 111111110, 编码后得到4 位反码, 经74AC04 反相后送到74LS247, 由74LS247 驱动LED数码管, 正确时能显示0~ 9。

输入011111111~ 111111110, 编码后得到4 位反码, 经74AC04 反相后送到74LS247, 由74LS247 驱动LED数码管, 正确时能显示0~ 9。

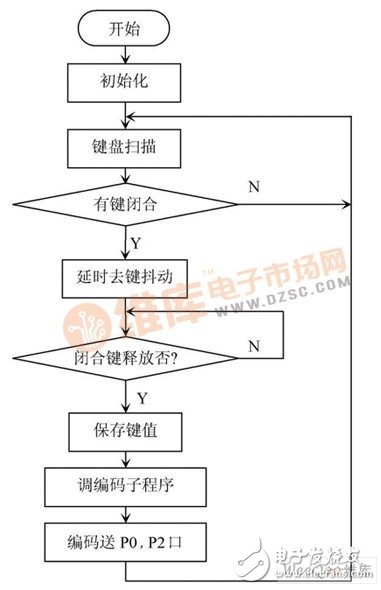

软件设计由初始化、键盘扫描、编码程序三部分组成。开始进行初始化, P0、P2 口按复位状态附值输出,LED 无显示。然后4 ! 3 阵列式键盘开始进行扫描, 当判断有键按下时, 延时去键抖动, 判断是否务抖动, 当确定判断是有键按下时, 等待闭合键释放, 保存键值。根据键值调用编码程序, 将表1 对应的编码送到P0, P2口输出, 主程序流程图如图3 所示。

图3 主程序流程图。

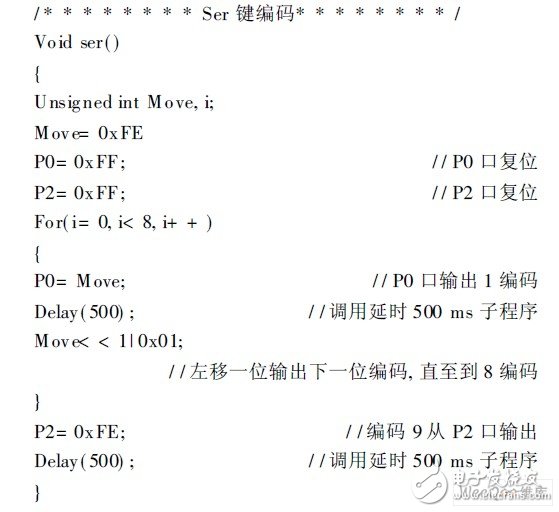

当按Ser( 顺序序列) 键时, 依次按1~ 9 编码值送至P0, P2 口, 间隔0. 5 s 输出。Ser 编码编码子程序如下:

Proteus 是一个基于Pro Spice 混合模型仿真器的,完整的嵌入式系统软、硬件设计仿真平台。编码译码显示电路能很方便地在此平台上进行调试和仿真, 延时时间同选用的单片机和所用晶体振荡器有关, 在调试时须注意。

5 结 语提出了一款编码译码显示实验电路设计, 其控制系统和编码信号发生器采用89C51 单片机实现, 经Proteus 仿真和实验调试结果来看, 大大改善了电路的性能, 电路制作方便、 *** 作简单, 在数字逻辑电路实验教学中具有一定的推广价值, 电路主要不足是不能实现故障自动检查, 如果能对电路故障进行自动检测, 电路性能将更加完善。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)