频率合成主要有三种方法:直接模拟合成法、锁相环合成法和直接数字合成法(Direct Digital Frequency Synthesis,一般简称DDS)。直接模拟合成法利用倍频、分频、混频及滤波,从单一或几个参考频率中产生多个所需的频率。该方法频率转换时间短,但是体积大、功耗大,目前已基本不被采用。锁相环合成法通过锁相环完成频率的加、减、乘、除运算。该方法结构简化、便于集成,且频谱纯度高,目前使用比较广泛,但存在高分辨率和快转换速度之间的矛盾,一般只能用于大步进频率合成技术中。DDS 是近年来迅速发展起来的一种新的频率合成方法。该方法与前两种方法相比,这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,可以实现可编程和全数字化,控制灵活方便,并具有极高的性价比。

目前虽然有很多专用DDS 芯片,但控制方式却是固定的,在某些场合,专用的DDS 芯片在控制方式、置频速率等方面与系统的要求差距很大,不一定是我们所需要的。而用高性能的FPGA 器件设计符合自己需要的DDS 电路是一个很好的方法。可编程逻辑器件以其速度高、规模大、可编程,以及有强大EDA软件支持等特性,十分适合实现DDS 技术。

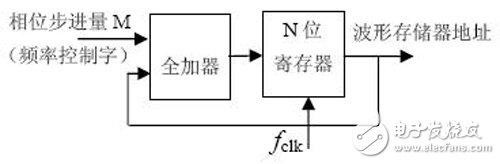

DDS 的原理框图如图1,控制电路按照一定的地址关系从存储器中读取数据,进行数摸转换,就可以得到一定频率的输出波形,再通过滤波器对输出波形进行平滑处理。

图1 DDS 原理框图

基于FPGA 的DDS 控制电路的实现有采用相位累加和比例乘法器两种方案,下面将分别介绍。

二.采用相位累加控制实现DDS1.工作原理

电路如图2 所示,相位累加器由N位加法器与N位相位寄存器级联构成,类似于一个简单的加法器。每来一个时钟脉冲fclk,加法器就将频率控制字M 与相位寄存器输出的累加相位数据相加,然后把相加后的结果送至相位寄存器输入端。相位寄存器在下一个时钟的作用下就将加法器在上一个时钟作用后产生的新相位数据反馈到加法器的输入端,以使加法器继续将相位数据与频率控制字M 相加。频率控制字M 由累加器累加以得到相应的这个相位数据将作为取样地址值送入的波形存储器,波形存储器根据这个地址输出相应的波形数据。最后经D/A 转换器和低通滤波器将波形数据转换成所需要的模拟波形。

图2 相位累加器

当相位累加器累加满量时,就会产生一次溢出,完成一个周期性的动作,这个周期就是合成信号的一个周期,累加器的溢出频率也就是DDS 的合成信号频率。

根据以上原理,输出信号频率与累加器时钟fclk, 累加器位数N,相位增量M 的关系为f0=(fclk, • M )/ 2N 。其中:采样点为2N/M,若fclk,一定,f0 越高,采样点数越少;最小步进为fclk/2N,达到最小步进值时,采样点数最多。设计中根据所要求的最高频率和最少采样点数可确定需要的fclk;根据最小步进和fclk,可确定N 的位数;根据最高输出频率和最小步进可确定M 的位数。

2.设计实现

如要求设计产生频率范围为0HZ~~160KHZ,频率的最小步进为5HZ 的信号。

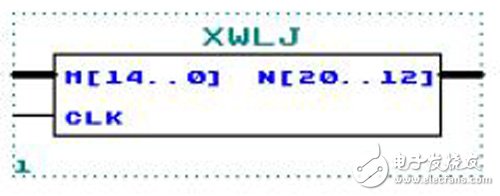

根据公式可计算出fclk、N、和M 。f0 若达到160KHZ,采样点数达64 点,则累加器时钟fclk 为不小于10.24MHZ;为实现5HZ 的步进,此时采样点数最多,有 5= fclk / 2N ,得到N=21,即累加器为21 位;最终输出频率与相位增量M 的关系为f0 =5M,由于最高达到160KHZ,则M≥160000/5=32000,而215=32768,所以选择相位增量的位数为15 位。相位累加器XWLJ 采用VHDL 设计,其高九位给波形存储器作为地址,根据以上要求的VHDL 设计,编译成功后自动生成的逻辑符号如图3 所示。

图3 XWLJ 逻辑符号

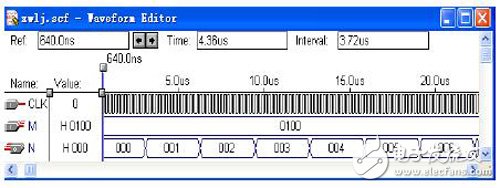

若当频率控制字为M=0100H 时,其仿真波形如图4 所示。可以看出,N 的输出高九位按设计要求实现了相位累加的功能。

图4 相位累加器仿真波形

三.采用比例乘法器控制实现DDS1.比例乘法器工作原理

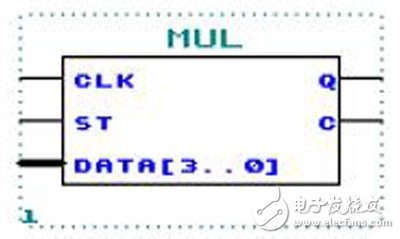

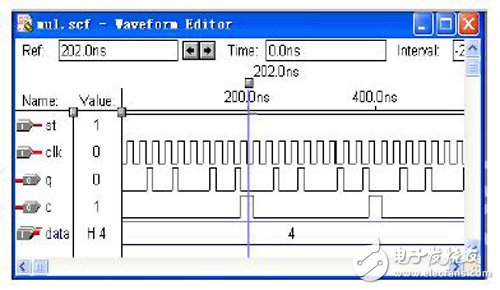

根据硬件比例乘法器(CC14527)的原理,我们对其进行VHDL 设计实现。其完成的功能为:ST为片选信号,当ST 有效时,在CLK 每十个脉冲中输出端Q 将输出DATA[3..0](0~9)个脉冲,同时在CLK 满10 个脉冲时,C 端产生一个脉冲控制信号。在Max+plusⅡ下编译成功后自动生成的逻辑符号MUL 如图5 所示。其仿真波形如图6,可以看出,当data 为4,在clk 十个脉冲中, q 输出4 个脉冲,在CLK 满10 个脉冲时,C 端产生一个脉冲控制信号,完全实现了比例乘法器功能。

图5 比例乘法器的逻辑符号

图6 比例乘法器仿真波形

2 设计实现

在两个比例乘法器级联时,令高位输入数据q0,低位输入数据q1,在每10 个脉冲中高位输出q0个脉冲,同时高位C 端禁止低位CLK 进入,当高位满10 个脉冲后高位C 端允许低位CLK 进入1 个脉冲,这样在100 个脉冲中整体上将输出10q0+q1 个脉冲。于是在n 级级联后,若输入频率为f,则输出脉冲频率为[10 n-1q0+10n-2q1+…+10q(n-2)+q(n-1)]f/10n。

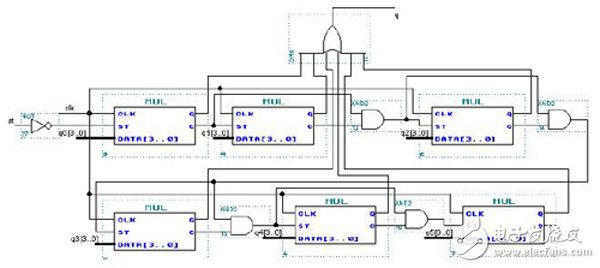

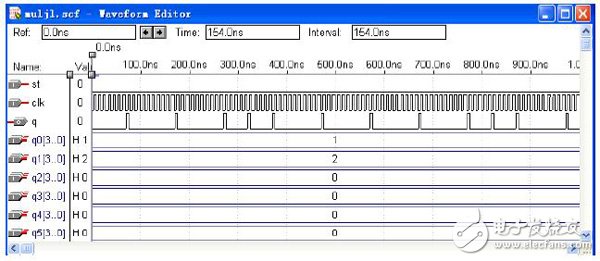

在Max+plusⅡ软件环境下,对上面采用VHDL 语言已经实现的比例乘法器模块MUL,采用6 级级联产生DDS 控制电路顶层图如图7 所示, 为了清楚地显示设计功能,仿真时q0 取1,q1 取2,其仿真波形如图8 所示,可以看出,在CLK 的100 个脉冲中,q 输出12 个脉冲。在给定输入下,完全实现了设计的功能。

图7 MUL 级联构成的DDS 控制电路

图8 MUL 级联构成的DDS 控制电路的仿真波形

若在单片机的控制下,FPGA 接收单片机传送过来的用户要求的波形数据,及其频率数据,并送到FPGA 以产生所需要的输出频率值。若时钟信号为16MHz 时,则产生的频率为实际所置频率的16 倍。在用户给定某一频率后,通过单片机将其乘8 后再送给FPGA,乘法器再将其扩大16 倍,得到用户预置频率128 倍频,故可以对波形的采样点达128 个,提高波形准确度,很容易实现低值的频率步进,步进可以降低到1Hz。

3. 结论实践证明,通过FPGA 实现的DDS 控制电路与其它的控制芯片如单片机等相结合,可以准确、灵活和方便地实现任意信号发生电路的设计。 以上两种控制方案,只要累加器位数和比例乘法器级联足够多,就可以实现频率的步进小,产生的频率信号准确,稳定性好,频率的分辨率高,频率转换快,容易控制。FPGA 的功能完全取决于设计需求,具有相当大的灵活性,比购买专用DDS 芯片具有很高的性价比。基于FPGA 的DDS 控制技术,将在现代化电子系统和仪器仪表工业等领域广泛应用。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)