许多年轻的工程师在工作中考虑潜在设计选项时首先想到可编程逻辑。然而,随着对可编程逻辑的日益依赖也给教授电路设计带来了经常被忽略的一些问题,这使许多年轻的工程师在创建系统时,没有意识到现在有许多可选择的技术能够解决他们在设计方面的挑战。在许多情况下,这种行业选择的知识缺乏与实践设置经验的缺乏是有关系的,这种专门技术的缺乏直接影响到他们设计高性能、低成本产品的能力。

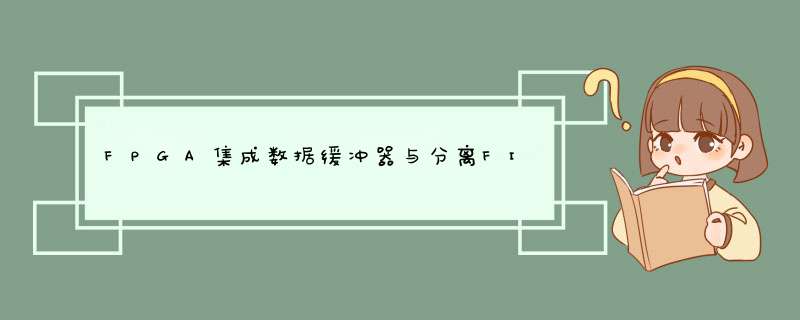

图1:用于高性能路由器的40Gbps解决方案

内嵌的缓冲存储器

这种趋势的最好例子就是内嵌的数据缓冲存储应用。多年来,FIFO和多端口存储器一直是资深设计工程师创建高性价比的数据缓冲子系统的事实上的标准。然而,随着FPGA存储器密度的增加,设计工程师们已经选择使用片上存储器替代分立的FIFO或多端口存储器的功能。

对高级系统来说,把分立的FIFO或多端口存储器功能集成到FPGA似乎很有意义。将多个数据缓冲器和数据控制功能集成一个芯片中,提供了一个更为优秀的解决方案。其吸引力在于能使设计工程师减少元件数量和最大限度地缩小电路板的空间需求。为了帮助设计工程师,FPGA供应商提供了一系列标准化的设计构建模块来加速开发进程。

但是,优秀的解决方案需要一定的成本,高密度的FPGA并不便宜。当数据总线速度超过100MHz,同时需要更高密度的缓冲器时,那就要更加昂贵的 FPGA。性能也可能成为一个问题。当工程师把FIFO或多端口存储器功能集成到可编程逻辑单元时,一些性能局限并不是显而易见的。在许多情况下,采用分立元件或结合小型FPGA可以提供更为理想的解决方案。

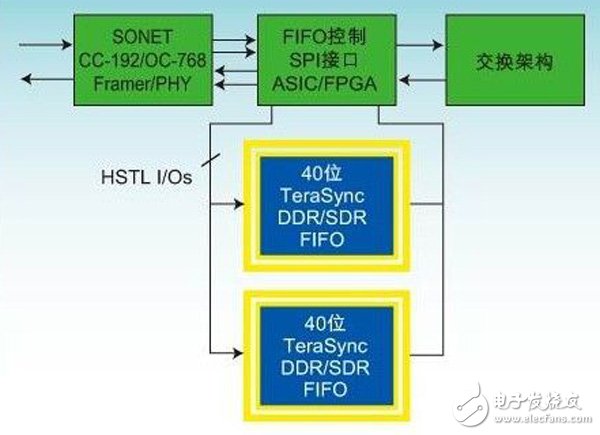

多端口存储器有类似的发展过程。设计工程师可选择每个端口不同总线宽度,支持8到72位之间的器件。这些器件在同步模式下速度高达200MHz或在异步模式访问速率达 10ns,同时密度高达36Mb。目前器件可支持的内核电压范围为5V、3.3V、2.5V或1.8V,I/O电压为5V、3.3V、2.5V,可选择 3.3V/2.5V或1.8V。还有许多特殊功能可供使用,包括全边界计数器(full-boundary counter)、独立字节使能、冲突检测、中断、旗语和忙仲裁。

内嵌数据缓存的性能局限性

当一直被教育使用 FPGA的工程师设计数据缓冲子系统时,他们自然地倾向于把FIFO设计成FPGA。然而许多人没有意识到,因为他们设计中的FIFO数量的增加使他们面临着性能局限性的问题。通常,这些工程师使用来自主要供应商的工具,自动地将多FIFO映射到单个物理存储器模块中,在多个特定用户FIFO之间产生时间域复用所需的逻辑。然而,因为每个独立的FIFO端口必须一起进行复用,所以每个FIFO端口的最高工作频率与映射到设计中的FIFO的数量成反比。

图2:低功耗双端口器件是多媒体智能电话的理想之选

当每个FIFO器件利用其时钟独立运行时,数据、控制输入和状态标记、FIFO之间总的存储带宽是共享的。当一个FIFO器件的读写 *** 作启动时,定序器(sequencer) 电路会在快速的时分复用(TDM)时钟域存取物理数据。之后,定序器电路快速访问TDM时钟域的物理存储器。然后,定序器把信息传回到FIFO端口的时钟域完成存储存取。因为时钟域的传输,FIFO器件的性能受到定序器电路的速度和使用的FIFO数量固有的限制。实际上,一些领先FPGA供应商推荐需要在高性能设计中把他们器件的FIFO数量控制在10个之内。

在把一个FPGA配置成双端口时,也会有很多与性能相关的问题。在很多这种应用中,FPGA往往和ASIC连接在一起。性能受三个主要因素控制:内在速度或从双端口写入和读取信息的速度、建立时间或数据在ASIC输入变得稳定需要的时间,以及最高速度或外部ASIC获得双端口信息的速度。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)