摘要: 一种采用AD9789与FPGA相结合,在FPGA上实现全数字QPSK射频调制的方案。介绍了AD9789的接口设计及配置流程,并给出了设计实例。

DVB-S标准只是规定了信道编码及调制方式,没有提供具体的射频调制方案,DVB-S标准要求载波的频率范围为950 MHz-2150 MHz,由于受到FPGA内部资源运算速度的限制,一般只能实现中频调制[1]。传统的射频调制是在中频调制后加模拟上变频,如中频调制之后采用AD8346[2]进行射频调制,但这样就增加了设计的复杂度及成本。本文采用ADI公司最新推出的AD9789与FPGA相结合的方法实现了全数字DVB-S标准射频调制。

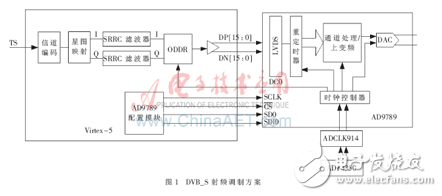

AD9789[3] 14 bit TxDAC芯片内部集成了QAM编码器、内插器和数字上变频器,可为有线基础设施实现2.4 GHz的采样率。AD9789 TxDAC支持DOCSIS-III、DVB_C 2个标准,并不支持DVB-S标准。配置选项可以设置数据路径来为QAM编码器和SRRC滤波器设置旁路,从而使DAC能够用于诸如无线基础设施等多种应用中。本文就是利用这一点实现了DVB_S的射频调制,在FPGA内部实现DVB-S信道编码[3](随机化、RS编码、卷积交织、卷积压缩编码)、星图映射、SRRC 滤波器(滚降系数为0.35),经ODDR模块给AD9789提供复数数据。其射频调制方案如图1所示。

2 可变符号率的设计

DVB-S调制器符号率一般支持1 MS/s~45 MS/s可调,这就需要对TS流进行速率调整。整个DVB_S信道编码有2次速率的变化:(1)RS编码,它将188的包结构变成204的包结构,数据输出的速率为输入的204/188倍。(2)卷积压缩编码,由于卷积压缩编码采用不同的编码比率,如1/2、2/3、3/4、5/6、7/8,对应的输出数据速率就变成输入数据速率的1、3/4、2/3、3/5、4/7倍,针对符号率的设计,本文提出了符号率的设计公式:FBAND=A×204/188×8×1/2×(N/N-1),其中A为TS流的输入数据速率,N的取值为2、3、4、6、7,之所以乘以8是因为在卷积编码时要进行数据的并串转换。

本文采用插空包的方式实现RS编码速率调整,其设计思路是在信道编码之前对TS流进行一次速率调整,将188的数据包变成204的数据包,这样大大简化了后端的设计,具体的 *** 作就是通过FIFO实现,由于TS流速率慢,所以先写FIFO,等到写满一半,开始读,读的时候每次只读188个数据,然后再在其后添加16 B数据,添加0即可,这样就变成了204个字节的包结构。由于读的速率很快,有可能读空,所以要判断FIFO内部所剩下的数据,当不满188 B时,就插入204 B的空包,这样可以保证速率调整之后的数据是连续的。符号率的设计公式变成:FBAND=B×8×1/2×(N/N-1),只需要改变B及N的值就可以实现符号率的可变。

针对卷积压缩编码速率调整,本文采用重配置DCM[4]与FIFO结合的方式实现,由于调制采用不同的编码率,导致输出的数据速率是可变的,这就使得数据的输出时钟是输入时钟的非整数倍,很难做到小数分频,所以提出了用重配置DCM的方式提供可靠的时钟对应关系。经卷积压缩编码后的数据输出是不连续的,为了便于后续数据升采样的处理,通过一个FIFO将数据打成匀速的。

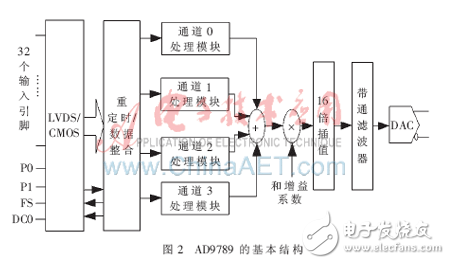

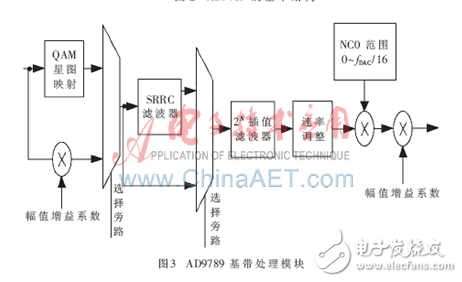

3 AD9789基本结构[5]AD9789 包含一个用于器件配置和状态寄存器回读的 SPI(串行外设接口)端口。灵活的数字接口可以适应4 bit~32 bit的数据总线宽度,并且可以接收实数或复数数据,最多可接收4路输入信号。每一路信号最大能经过5级半带插值滤波,插值之后的数据与NCO生成的正余弦信号相乘,再经过通道增益变化,4路信号相加后再通过总增益调整、16倍插值和带通滤波器实现数字上变频,最后经数模转换输出,其原理如图2所示。4个通道的基带处理模块内部结构相同,如图3所示。在本设计中,旁路掉QAM编码器和SRRC滤波器,经过5级半带插值后,通过调节P/Q值,可实现不同符号率的调整。

4 AD9789上变频原理及配置流程[5]

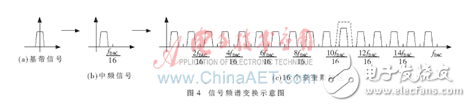

基带信号经过插值后与NCO生成的正余弦信号相乘,从而把基带信号频谱调制到0~fDAC/16之间完成基带调制,即实现图4(a)~图(b)的转换。经过16倍插值滤波器后,形成16个奈奎斯特区,后15个区内的频谱为第1奈奎斯特区基带调制信号的镜像频谱,通过配置带通滤波器的中心频率,可滤除不需要的15个镜像,得到要想的调制信号,如图4(c)所示。AD9789的这种特殊架构,使得输出的调制信号频率范围为0~fDAC,而fDAC最高可达2.4 GHz,完全可以满足DVB-S标准L波段输出的要求。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)