利用FPGA及其片上32位微处理器内核MicroBlaze,构建雷达目标跟踪系统,硬件实现的高速并行性保证了多目标跟踪的实时性,微处理器CPU强大的控制协调功能保证系统的正常运行。针对多目标波门排序这一难点,本文提出了利用顶层软件排序的方法,降低了难度和运算量,提高了灵活性,很好的解决了问题。

1 引言随着集成电路的不断发展,可编程逻辑器件FPGA因其功能强大,设计灵活,开发周期短等特点,受到越来越广泛的应用.目前在信号处理领域应用系统的设计中,广泛采用的是“FPGA+DSP”的体系结构,其中FPGA完成控制简单,运算量大的算法处理工作,DSP作为系统的处理器进行系统控制,任务协调等工作.然而这种系统需要处理DSP与FPGA之间的通信和数据交换,增加了系统体积和实现复杂度,如果能利用FPGA的逻辑资源来完成这些控制功能,不但提高了系统集成度,也提高了系统的性能.目前FPGA不断朝着实现更高密度,更大容量的千万门级系统发展,同时MCU,DSP,MPU等嵌入式微处理器以IP核的形式嵌入到FPGA中,使得在FPGA上实现算法和控制功能的集成即可编程片上系统(System on Programmable Chip)成为可能.

本文介绍了利用Xilinx最新推出的Spartan 3E系列XC3S500E芯片,及其支持的微处理器软核MicroBlaze构建雷达目标跟踪系统,完成了对多目标的跟踪,波门排序和信息管理存储以及与主机的通信.

2 MicroBlaze简介MicroBlaze 处理器内核是针对FPGA器件而优化的功能强大的标准32位RISC处理器,运行速度高达150MHz,采用哈佛体系结构,具有独立的32位指令总线和32位数据总线.这两种总线又分为局部存储器总线(Local Memory Bus,LMB)和IBM的片上外围总线(On-chip Peripheral Bus,OPB)两类.LMB总线可提供对片上双端口Block RAM的高速访问,OPB总线可提供对片上外设,存储器,以及基于硬件描述语言编写的算法模块的访问,MicroBlaze可以响应软件和硬件中断,进行异步处理.

3 MicroBlaze的开发环境和开发流程应用EDK(嵌入式开发套件)可以进行MicroBlaze IP核的开发。工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试工具等。EDK中提供一个集成开发环境XPS(Xilinx 平台工作室),以便使用系统提供的所有工具,完成嵌入式系统开发的整个流程.EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART、中断控制器、定时器等。利用这些资源,可以构建一个较为完善的嵌入式微处理器系统。

图1 MicroBlaze 内核结构图

MicroBlaze的开发流程大致有以下四步:

1利用微处理器硬件规范文件(MHS)和微处理器软件规范文件(MSS),定义软件和硬件系统。

2利用系统库生成器,建立相关的库函数和驱动函数,并利用gcc编译器编译编写的C程序源代码。

3利用平台生成器,生成系统网表,HDL代码,片上块存储器初始化代码。

4利用系统硬件模型,综合后的ELF文件和用户约束文件,应用FPGA综合实现工具生成比特流,并利用JTAG接口下载到硬件上进行调试和实现。

图2 MicroBlaze 开发流程图

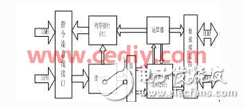

4.系统总体设计方案系统总体框图如图三所示,多目标跟踪模块是基于硬件描述语言的底层算法中心,完成多目标的识别,跟踪和预测,它按照OPB总线协议挂在总线上与MicroBlaze通信,MicroBlaze通过配置寄存器,完成对它的控制;A/D转换器采用TLC5540,完成对回波信号的数字化;锁相环CD4046完成对方位脉冲的分频锁相;串口模块完成与主机的通信和交互;中断控制器实现对多中断的协调管理,配置优先级;FLASH采用SST25LF080A,完成最终程序的固化和上电初始化;片上块RAM完成程序的存储和雷达多目标相关信息的存储,基于MicroBlaze的顶层软件算法完成对这些模块的控制和协调,同时完成多目标波门的排序。

图3 系统总体实现方案

5.MicroBlaze在波门排序中的应用当进行多目标跟踪时,需要对多个目标信息进行存储,同时必须保证多目标波门数据,按其方位和和距离的大小顺序排列,这样才能保证随着雷达方位和距离的扫描,依次对各个目标进行连续的自动跟踪.完全基于硬件的排序,不但时序复杂,而且灵活性很差,在实际中很难实现,一直是全自动跟踪系统实现的难点,而本文通过MicroBlaze顶层算法实现,利用C语言强大的指针功能,很好的克服这些困难.下面就这个问题进行详细的介绍.

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)