在高速电路系统设计中,差分串行通信方式正在取代并行总线方式 ,以满足系统对高带宽数据通信的需求。RockeTIO是Virtex2 Pro以上系列中集成的专用高速串行数据收发模块,可用于实现吉比特的数据传输,适用于多种高速数据传输协议。依据实际工程应用需求,提出了基于RockeTIO的高速串行数据传输系统解决方案,实现了每通道2.5 Gb/s的传输速度。最后介绍了RockeTIO在Aurora和PCI Express协议实现中的应用,并总结了高速通信系统的共性特征。

引言随着电子系统对速度以及精度要求的提高,高速串行数据通信模式正在逐步取代传统的并行总线式结构。并行总线结构由于其固有的缺点,在速度上的提升空间已经很小。

① 并行总线在印制电路板上要占用大量的空间,在电路系统日益小型化的今天给系统的设计带来很大困难。如PATA66以上的PATA数量达到了80根,使得电路板的布线极为困难。

② 并行总线由于在布线时很难保证每条线路长度与电气特征一致,导致信号到达时间不同,在较高的工作频率下很难实现完全同步,以致出现信号偏移。这使接收器难以确定采样时间,容易造成数据错误。

③ 由于寄生电容的影响,在并行的两条数据线中容易产生串扰,甚至改变信号原有真实电平。采用地线进行屏蔽可以在一定程度上消除串扰,但同时也造成总线线路数目的急剧增加。

④ 并行总线参考电平为地电平,容易受噪声干扰。同时由于在总线上“0”、“1”分布不均匀,在信号收发器之间易造成直流偏置,造成信号噪声容限降低。

相比而言,高速串行总线采用差分对的形式,并且在发送端与接收端之间采用点对点的连接结构。差分信号经过编码,消除信号序列中直流分量,从而可以提高噪声容限。同时,在信号序列中插入时钟信息,信号中携带时钟,解决了信号偏移问题。

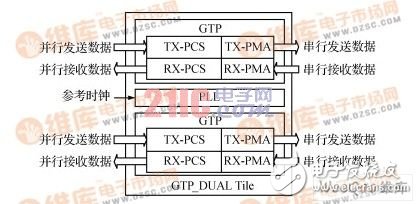

1 RockeTIORocketIO收发器是在Virtex2 Pro以上系列FPGA中集成的专用串行通信模块,在使用时不占用FPGA其他逻辑与片上存储资源。在Virtex5 LXT和SXT系列FPGA中,RocketIO称为GTP,每两个GTP共用一个PLL,组成一个GTP_Dual。其结构框图如图1所示。

图1 GTP_Dual Tile结构框图

每一个RocketIO收发器均具有如下特征:

◆ 具有可配置终端、电压摆幅与耦合的电流模逻辑串行驱动或缓冲器。

◆ 可编程发送预加重和接收均衡,以实现最优信号完整性。

◆ 100 Mb/s~3 Gb/s的线速范围,线速在100 Mb/s~500 Mb/s区间时具有可选的5倍过采样功能。

◆ 可选的嵌入式PCS功能,例如8位/10位编码、逗号对齐、通道绑定以及时钟校正。

◆ 最小化的确定性数据通道延迟。

◆ 对PCI Express、SATA、传输等协议的支持。

从应用上讲,RocketIO处于数据传输协议的物理层,用以实现最基本的数据通信环境。其主要功能可以概括为:将输入的并行数据经过编码,转化为高速的差分串行信号。在实际应用中,输入时钟、PLL参数设置以及PCB线路的设计与布局是影响数据传输效果的最重要因素。

1.1 输入时钟

RocketIO有三种时钟输入方式:专用差分时钟、共享邻近GTP_Dual的时钟、以及使用FPGA内部时钟。Rocket I/O GTP时钟输入方式如图2 所示。

图2 Rocket I/O GTP时钟输入方式

使用专用差分时钟时,差分的时钟信号通过输入差分缓冲器变为单端时钟,输入到GTP_Dual Tile中的PLL,当使用的时钟源精度满足要求时具有最优的时钟稳定性。

从相邻GTP_Dual Tile获得时钟时需要使用GTP专用的时钟通路,但此时GTP_Dual与提供时钟的GTP_Dual Tile间隔的GTP_Dual Tile个数不能超过两个,即每对差分输入时钟最多可驱动7个GTP_Dual Tile。

相比于上述两种时钟输入方式,从FPGA内部获得时钟时钟精度最差。这是因为光纤,FPGA内部使用的时钟经过逻辑电路以及BUFG或BUFR缓冲后,会引入较大的时间抖动。但由于在FPGA内部可以灵活变换参考时钟频率,因此在速度与精度要求不太高的场合可采用FPGA内部时钟。经实验验证,对于误码率要求在1‰以下的应用,从FPGA内部获得的时钟信号可以满足要求。

1.2 PLL参数设置

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)