通过前面的PL DMA设计,在SDK中运行,很正常的没有运行起来(block design与source desing都是自己手敲,明显的错误已经改正,能够生成bit文件启动SDK调试)。

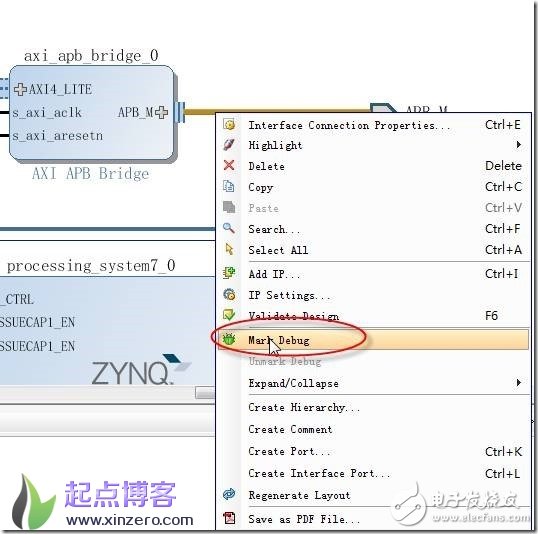

首先在PL部分调试,作为PL DMA的控制APB总线,将其设置为Mark Debug,如下图所示。

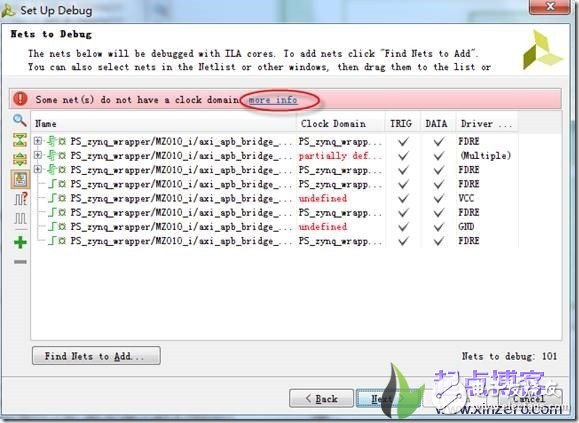

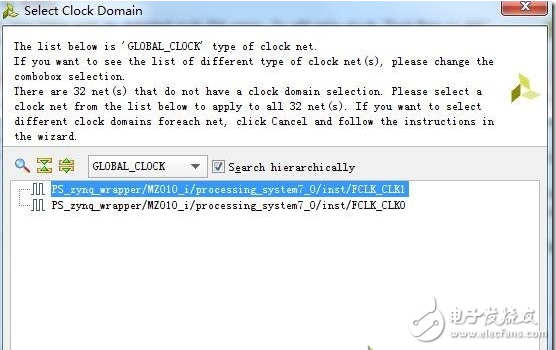

然后重新综合,综合完成,不进行implemenTIon,在综合菜单下面找到“Set Up Debug”,进行ILA配置,出现下图的设置窗口。

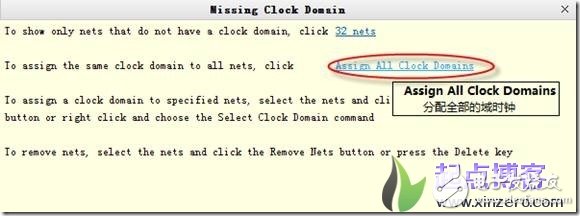

在上图中点击“more info”,出现提示,部分网表没有设定时钟。

全部选择,然后右键选择时钟,如下图所示

选择FCLK_CLK1时钟,因为此时钟为150Mhz,而APB总线时钟为FCLK_CLK0为50Mhz,用150Mhz时钟采样便于观测,然后一路默认完成。然后再生成bit文件。

调试过程

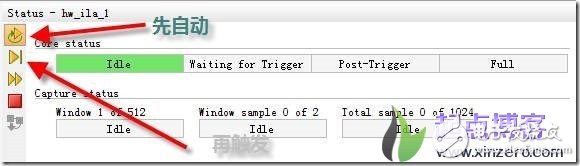

先在SDK中启动PL DMA PS部分的测试程序,停在main函数处。

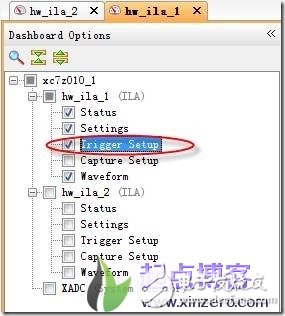

然后在vivado中program device,启动ILA调试窗口。

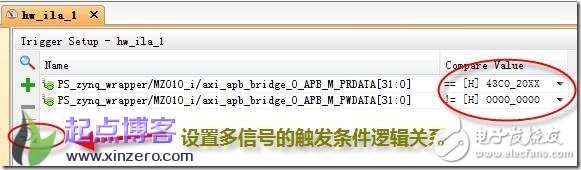

选择“Trigger Setup”,出现“Trigger Setup”窗口,进行触发条件设置。

上图中可以通过“+”添加多个监测信号,通过后面的Compare Value设置触发条件。当有多个触发条件时,可以通过左则的逻辑符号进行设置它们的触发关系。

选择上图中触发

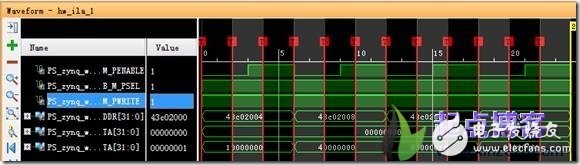

然后到SDK下运行测试测试,在对APB总线对应的地址空间进行读取 *** 作后,出现下图所示的调试窗口信息。

从图中数据与PS部分写入数据的比较,APB总线的数据是正常的。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)