摘要

本作品是基于FPGA的ADC0809采集控制电路。ADC0809是美国国家半导体公司生产的CMOS工艺8通道,8位逐次逼近式A/D模数转换器。其内部有一个8通道多路开关,它可以根据地址码锁存译码后的信号,只选通8路模拟输入信号中的一个进行A/D转换。

Abstract

This work is ADC0809 sampling control circuit based on FPGA. ADC0809 is produced naTIonal semiconductor CMOS 8 channel, eight successive approximaTIon A/D analog-to-digital converter. Its internal have A 8 channel mulTIplex switch, it can according to the address latch signal after decoding, only gate 8 analog input signals of an A/D conversion.

1. 设计任务

基于FPGA的ADC0809控制电路设计,并阐明其控制原理。

2. ADC0809简介

2.1. ADC0809主要特性

①8路8位A/D转换器,即分辨率8位。

②具有转换起停控制端。

③转换时间为100μs

④单个+5V电源供电

⑤模拟输入电压范围0~+5V,不需零点和满刻度校准。

⑥工作温度范围为-40~+85摄氏度

⑦低功耗,约15mW

2.2. ADC0809外部特性(引脚功能)

①ADC0809芯片有28条引脚,下面说明各引脚功能。

②IN0~IN7:8路模拟量输入端。

③D0~D7:8位数字量输出端。

④ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路

⑤ALE:地址锁存允许信号,输入,高电平有效。

⑥START: A/D转换启动信号,输入,高电平有效。

⑦EOC: A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

⑧OE:数据输出允许信号,输入,高电平有效。当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

⑨CLK:时钟脉冲输入端。要求时钟频率不高于640KHZ。

⑩REF(+)、REF(-):基准电压。

①①Vcc:电源,单一+5V。

①②GND:地。

2.3. ADC0809工作原理

首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。此地址经译码选通8路模拟输入之一到比较器。START上升沿将逐次逼近寄存器复位。下降沿启动 A/D转换,之后EOC输出信号变低,指示转换正在进行。直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。当OE输入高电平 时,输出三态门打开,转换结果的数字量输出到数据总线上。

3. 理论分析与计算

3.1. 系统设计原理

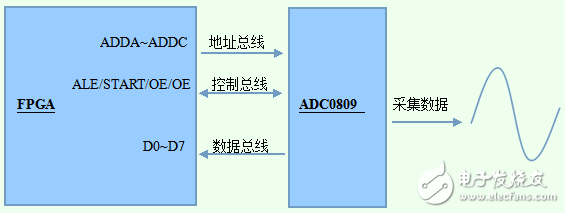

图3-1:系统设计原理图

工作原理:FPGA通过控制总线输入采集端口地址,此地址经ADC0809译码后选通8路模拟采集输入口之一。FPGA输出控制信号使AD的START脚信号出现高电平,上升沿将逐次逼近寄存器复位,下降沿启动 A/D转换。启动转换之后ADC0809的EOC脚输出信号变低,指示FPGA AD转换工作正在进行。直到A/D转换完成,EOC脚变为高电平,指示A/D转换结束,结果数据已存入锁存器。当FPGA检测到EOC脚变为高电平时,控制ADC0809的OE脚变为高电平,输出三态门打开,转换结果的数字量输出到数据总线上,再由FPGA存储起来。

3.2. AD计算分析

①转换量程:0~5V

②分辨率:参考电压为0-5V的话,ADC0809为8位AD,则每一位的电压值为(5-0)/255≈0.0196V

③转换时间: 取决于芯片时钟频率,本作品提供给AD的时钟频率为500KHZ,按官方资料知道AD转换时间为100μs(时钟为640KHz时),按此比例算出时钟为500KHz时的转换时间为130μs;

④采集最高频率:按130us转换时间来算,依据实际经验,在一个信号周期内采集6~7个点能使信号较好恢复原状,则能采集的最高频率大约为1Khz。

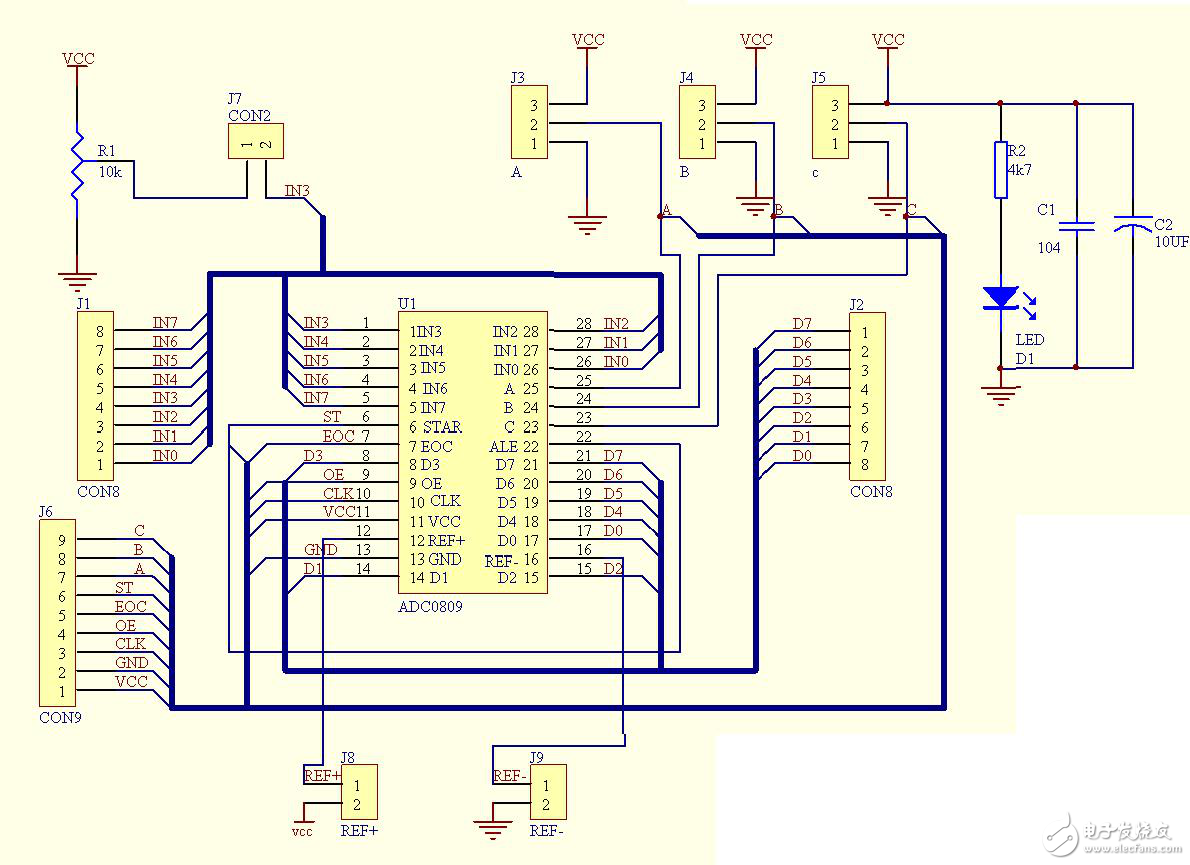

4. ADC0809硬件电路设计

图4-1:ADC0809硬件电路图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)