本文为大家介绍fpga数字钟设计。

数字钟的构成数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路。由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ时间信号必须做到准确稳定,通常使用石英晶体振荡器电路构成数字钟。

数字钟的工作原理振荡器产生稳定的高频脉冲信号,作为数字钟的时间基准,然后经过分频器输出标准秒脉冲。秒计数器满60后向分计数器进位,分计数器满60后向小时计数器进位,小时计数器按照“24翻1”规律计数。计数满后各计数器清零,重新计数。计数器的输出分别经译码器送数码管显示。计时出现误差时,可以用校时电路校时、校分。控制信号由1×5矩形键盘输入。时基电路可以由石英晶体振荡电路构成,假设晶振频率1MHz,经过6次十分频就可以得到秒脉冲信号。译码显示电路由八段译码器完成。

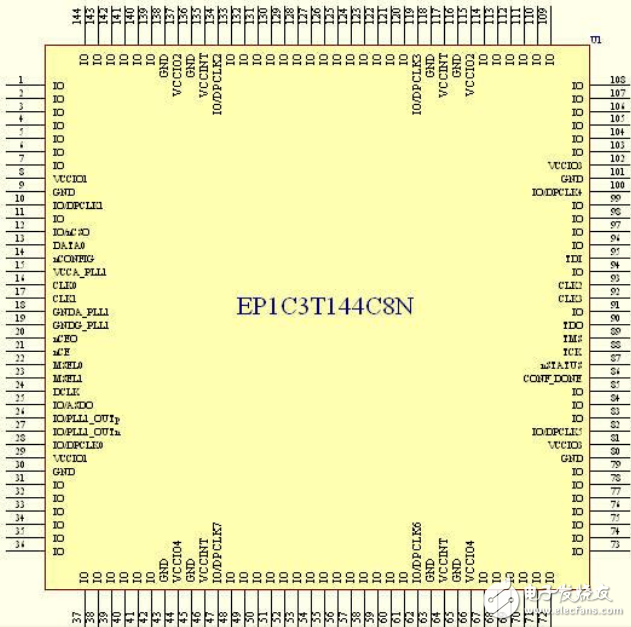

数字钟硬件电路设计 系统芯片的选取本系统拟采用Altera公司Cyclone系列的EP1C3T144芯片。选用该款芯片的原因是:

① Altera公司的Quartus II开发环境非常友好、直观,为整个系统的开发提供了极大的方便;

② 该FPGA片内逻辑资源、IO端口数和RAM容量都足够用,并且价格相对来说比较便宜,速度快,可以满足要求,且有很大的升级空间。

① 新的可编程架构通过设计实现低成本;

② 嵌入式存储资源支持各种存储器应用和数字信号处理器(DSP);

③ 采用新的串行置器件如EPCS1的低成本配置方案;

④ 支持LVTTL、LVCMOS、SSTL-2以及SSTL-3 I/O标准;

⑤ 支持66MHZ,32位PCI标准;

⑥ 支持低速(311Mbps)LVDS I/O;

⑦ 支持串行总线和网络接口及各种通信协议;

⑧ 使用PLL管理片内和片外系统时序;

⑨ 支持外部存储器,包括 DDR SDRAM(133MHZ),FCRAM以及 SDR SDRAM;

⑩ 支持多种IP,包括Altera公司的MegaCore以及其合伙组织的IP,支持最新推出的Nios II嵌入式处理器,具有超凡的性能、低成本和最完整的一套软件开发工具。

EP1C3T144引脚图如下图所示。

EP1C3T144引脚图

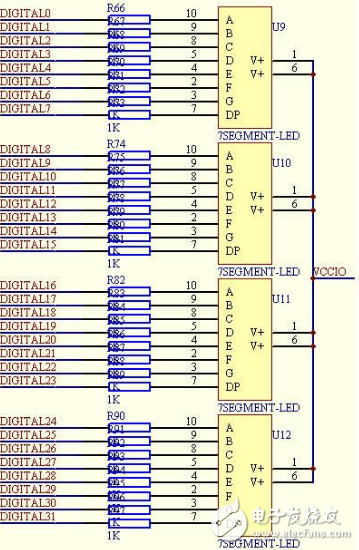

显示电路设计显示电路所选用4个数码管以静态显示驱动方式完成时、分显示。静态驱动是指每个数码管的每一个段码都由一个I/O端口进行驱动,其优点是编程简单,显示亮度高,缺点是占用I/O端口多。

显示电路原理图如下所示。

LED静态驱动显示原理图

LED静态驱动显示原理图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)