FPGA(Field-ProgrammableGateArray),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA芯片主要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

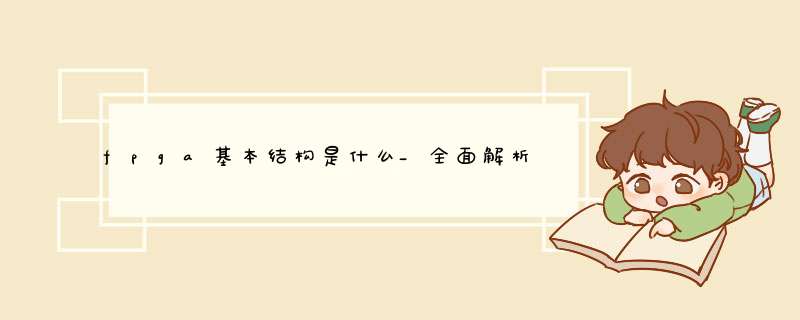

可编程逻辑块如果我们仔细观察FPGA封装的内部,我们将看到硅片(技术术语裸片)。可编程构造表现为可编程逻辑块阵列,如下图所示。如果我们用放大镜“放大查看”,我们可以看到这种构造由沉浸于可编程互连“海洋”中的许多逻辑“岛”(可编程逻辑块)组成。

如果我们进一步放大,我们可以看到,每个可编程模块都包含有许多数字功能。在这个例子中,我们可以见到一个三输入的查找表(LUT)、一个复用器和一个触发器,但重要的是我们要认识到,这些功能的数量和类型对不同系列的FPGA来说是会变化的。

触发器可以被配置(编程)为寄存器或锁存器;复用器可以被配置为选择一个到逻辑块的输入或LUT的输出;LUT可以被配置为代表任何所要求的逻辑功能。

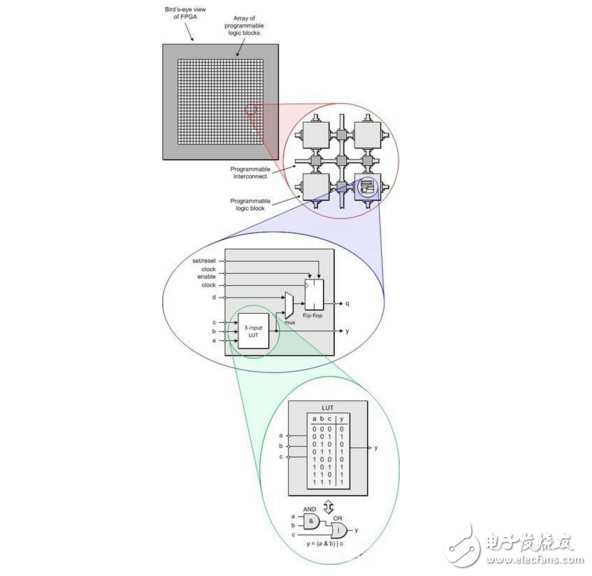

可编程输入/输出单元IOE

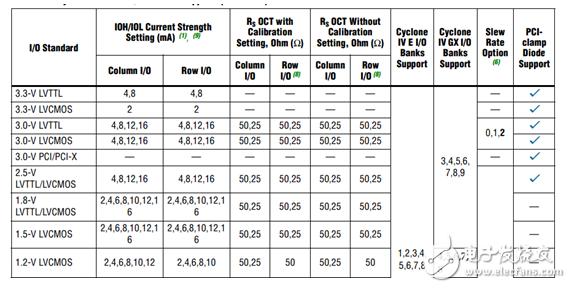

Altera器件IOE结构

Altera器件的输入输出结构:可配置成三态、输入/输出、双向IO

Altera器件中cyclone系列中的IOE结构是基本的输入、输出、使能的触发器结构。

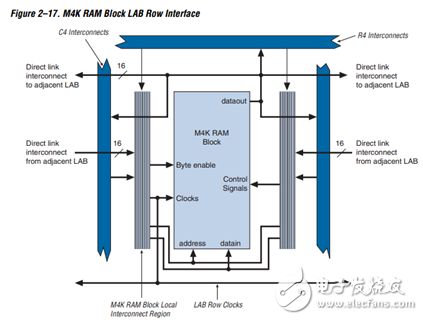

嵌入式块RAM(BRAM)大多数FPGA都具有内嵌的块RAM,这大大拓展了FPGA的应用范围和灵活性。块RAM可被配置为单端口RAM、双端口RAM、内容地址存储器 (CAM)以及FIFO等常用存储结构。RAM、FIFO是比较普及的概念,在此就不冗述。CAM存储器在其内部的每个存储单元中都有一个比较逻辑,写入 CAM中的数据会和内部的每一个数据进行比较,并返回与端口数据相同的所有数据的地址,因而在路由的地址交换器中有广泛的应用。除了块RAM,还可以将 FPGA中的LUT灵活地配置成RAM、ROM和FIFO等结构。在实际应用中,芯片内部块RAM的数量也是选择芯片的一个重要因素。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)