交流电磁场检测(AlternaTIngCurrentFieldMeasure-ment.ACFM)是一种基于电磁感应原理的主动式电磁无损检测技术,对导电工件表面及近表面裂纹的检测具有独特的优势。交流电磁场检测需要在被测工件表面感应出交变电流,当不存在缺陷时,感应电流均匀分布;存在缺陷时,缺陷对感应电流产生扰动,通过提取感应电流产生磁场的变化来确定缺陷的长度及深度等信息。

现场可编程门阵列(FieldProgrammableGateArray,FPGA)是近年来新型的高集成度数字器件,受到世界范围内电子工程设计人员的广泛关注和普遍欢迎,可以满足大多数专用检测系统的设计。本文以FPGA为开发平台设计频率可调的激励源模块,激励源由直接数字频率实现,合成频率适用于不同的被测材料,既可以满足交流电磁场检测系统的需求,又可以降低该系统的功耗和成本。并且FPGA的引脚丰富、存储区大,特别适合现场的实时检测系统,方便检测仪器的野外和高空 *** 作。

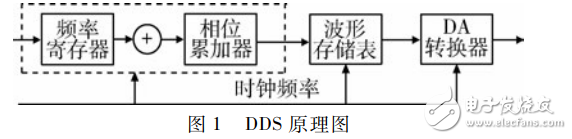

1、直接数字频率合成原理DDS或DDFS(DirectDigitalFrequencySysthesis)即直接数字频率合成,原理是将信号的完整周期预先做归一化处理,采样足够的点数存储,需要输出时通过时钟频率查找存储表地址对应的幅值输出给高速DA转换器,由低通滤波器输出模拟信号。典型的DDS原理如图1所示。波形存储表可以设置为正弦波)方波)三角波等波形。

假设正弦波信号的一个周期以2N次采样存储,fclk时钟频率fn为合成频率,T0为合成信号周期。并且假设累加器位数与地址位数相同,则控制合成频率有全采样和频率控制字采样两种方法。

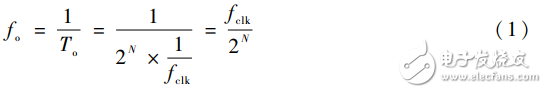

1.1、全采样时钟频率查找波形存储表的每一个地址,输出地址对应的幅值。则合成激励源的一个完整周期需要2n次查表,合成频率与时钟频率的关系如式(1):

式中:fn为合成频率,Tn为合成信号周期,fclk为时钟频率,2n为采样次数。由式(1)可知所有采样点都经过查找输出幅值时,通过改变时钟频率fclk即可合成不同频率的信号。

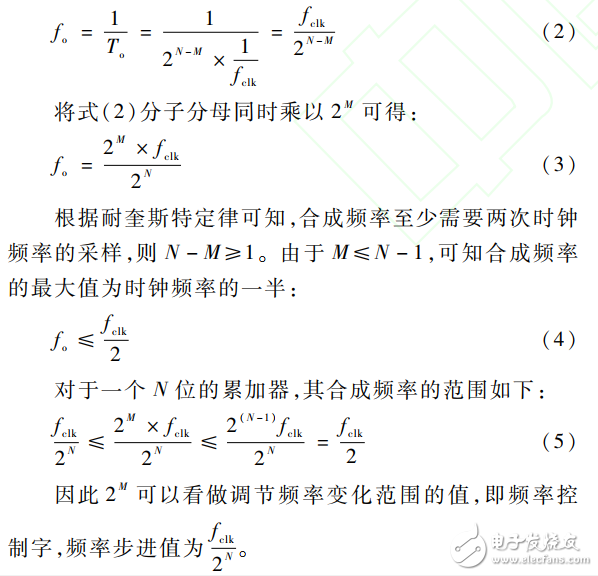

1.2、频率控制字采样在采样时钟频率一定时,已知波形存储表的长度不变,通过控制每次累加频率控制字的大小,改变查找表的次数,合成不同频率的信号。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)