在整个接收系统中,低噪声放大器总是处于前端的位置。整个接收系统的噪声取决于低噪声放大器的噪声。与普通放大器相比,低噪声放大器一方面可以减小系统的杂波干扰,提高系统的灵敏度;另一方面放大系统的信号,保证系统工作的正常运行。总之,低噪声放大器的性能不仅制约了整个接收系统的性能,而且,对于整个接收系统技术水平的提高,也起了决定性的作用。

1 低噪声放大器的设计指标

低噪声放大器的主要性能指标包括:稳定性、功率增益、噪声系数、增益平坦度等,在这些指标之中噪声系数和放大增益对系统性能的影响较大。因此对低噪声放大器的设计主要从稳定性、功率增益、噪声系数、输入输出电压驻波比等方面进行考虑。

1.1 稳定性

放大器电路必须满足的首要条件之一是其在工作频段内的稳定性。因为假如在设计和制造放大器时不谨慎从事,在微波频率上一些不可避免的寄生因素往往足以引起振荡。

所以为了保证电路的稳定性,主要采取以下措施:1)可以在源极引入负反馈,使电路处于稳定状态;2)采用铁氧体隔离器能稳定电路;3)在漏极串联电阻或∏型阻性衰减器,通常接在低噪声放大器末级或末前级输出口。而目前提高电路稳定性常用的是引入负反馈。

1.2 功率增益以及增益平坦度

放大电路的增益是放大电路最重要性能指标,也是设计放大电路的一个基本参数。因此在放大器的设计中增益指标的完成很是重要,功率增益主要有3种描述方式:可用功率增益GA,工作功率增益GP,转换功率增益GT。

增益平坦度对于低噪声放大电路来说,就是全频带范围内增益变化要平缓,不允许增益变化陡变。

1.3 噪声系数

噪声系数是LNA的另一重要指标,如果接收系统噪声系数过大,信号会被噪声埋没,致使接收系统的灵敏度减小。

1.4 驻波比

低噪声放大器通常用输入输出驻波比来表示输入输出信号的反射损耗,输入输出驻波比过大时不仅会损坏与低噪声放大器级联的器件还会使系统的增益起伏和群迟延变坏,因此低噪声放大器的输入输出驻波比应该满足一定要求,在一般系统中功率放大器的输入输出驻波比要小于2。

2 低噪声放大器的电路设计步骤

2.1 晶体管器件的选择和级数的确定

随着器件工艺技术的发展,人们开发了许多新型的半导体器件。除砷化钾场效应晶体管(GaAs FET)外,其佼佼者有高电子迁移率晶体管(HEMT)和异质结双极晶体管(HBT)。根据有关资料对3种主要器件的介绍和比较,我们知道HEMT可以提高跨导和电流密度,而且它能减小电路对工艺的敏感性,用HEMT制作的多级低噪声放大器已广泛用于卫星接收系统、电子系统及雷达系统。所以本设计选用HP公司的ATF-35176来进行低噪声放大器的设计。该器件是一种低噪声砷化镓PHEMT器件,适用于工作在2~18 GHz的低噪声放大器,满足设计要求。

另外考虑放大器的增益指标,由于一般的单管增益为9~12 dB,本设计的低噪声放大器目标需达到30 dB的增益,因此采用了三级级联放大电路。

2.2 晶体管直流分析

静态工作点的选择直接关系到放大电路的各种性能,所以结合ATF35176的使用手册上的数据对该晶体管的传输特性进行分析,选择合适的静态工作点。

2.3 偏置电路设计

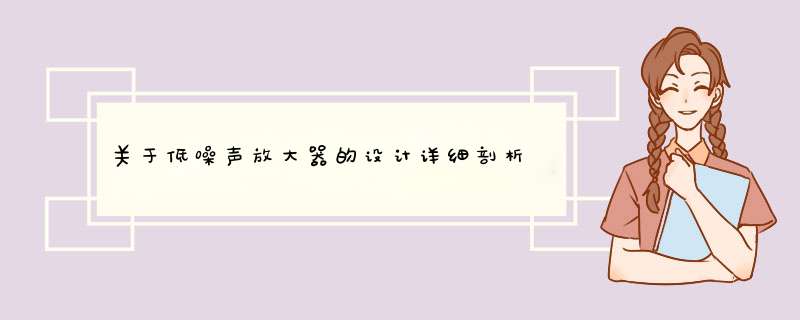

直流偏置电路根据外加电源可以分为2种:一种是双电源供电,另一种是单电源供电。单电源供电一般用于微波较低频段,单电源供电电路结构简单,但是对于噪声有一定影响。双电源供电一般用于比较高的微波频段,因为它可以在高频段提供较好的噪声特性。本论文采用的就是正负双电源供电,有利于低噪声设计,偏置电路如图1所示。

2.4 稳定性分析

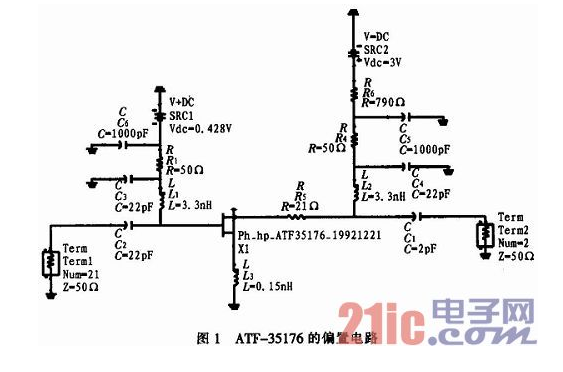

由于对偏置电路进行仿真得到稳定系数结果如图2所示,可以从图中看出在整个工作频段,放大器处于绝对稳定状态,所以无需进行稳定性设计。

2.5 输入匹配电路设计

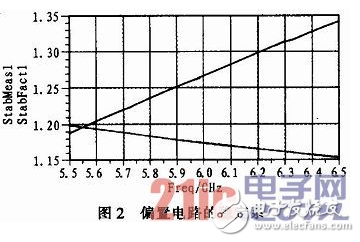

由于本设计采用多级放大,而第一级放大器的噪声系数对整个低噪声放大器电路的影响起这决定性作用,所以第一级放大器按照最小噪声系数对输入端进行匹配,采用smith圆图工具进行匹配,得到的输入匹配电路如图3所示。

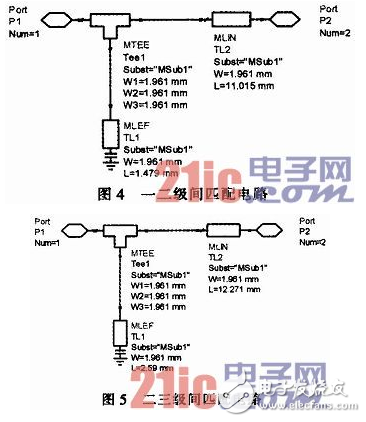

2.6 级间匹配

级间匹配电路的基本任务是使后级微波管输入阻抗与前级微波管输出阻抗匹配,以获得较大增益。因为第一级的设计是按最低噪声设计的,并没有使增益达到最大,所以第二级的噪声对整体的影响也是十分明显的,因此第一二级间的匹配也要偏重噪声系数,匹配电路如图4所示。而二三级间的匹配电路按照最大增益匹配设计,匹配电路如图5所示。

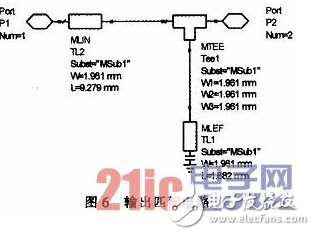

2.7 输出匹配电路设计

输出匹配电路的设计主要考虑增益和驻波比,基本任务是把微波管复数输出阻抗匹配到负载实数阻抗,从而提高增益和输出驻波比,匹配电路如图6所示。

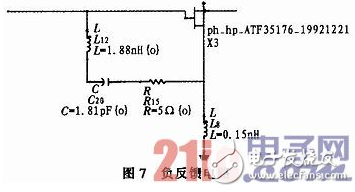

2.8 负反馈电路

为了适当改善放大器增益平坦度,在晶体管栅源之间采用负反馈网络所示,具体电路如图7所示。

实际上负反馈网络除了拓宽频带、改善增益平坦度外,还参与了匹配并改善输入输出驻波,其优点是便于充分发挥PHEMT电路的低噪声和高增益特性。

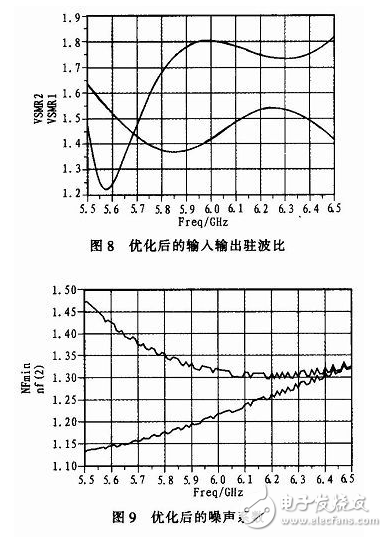

2.9 整体电路仿真优化

采用ADS中的优化功能,对原理图中微带线的长度、电容与电感值进行优化,最后得到满足要求的低噪声放大器。其仿真所得的驻波比、噪声系数以及增益分别如图8、图9、图10所示。

通过ADS仿真,噪声放大器工作在5.5~6.5 GHz波段,增益大于32.8 dB,噪声系数小于1.5 dB,驻波比小于2,满足设计需求。

3 结束语

文中主要采用三级放大,低噪声放大器选用ATF-35176晶体管,通过仿真分析,完成了偏置电路以及输入、级间和输出的匹配电路设计,并采用ADS软件进行全部电路的优化仿真,仿真结果表明,低噪声放大器工作在5.5~6.5 GHz波段,增益大于32.8 dB,噪声系数小于1.5 dB,驻波比小于2,达到了设计指标的要求。本设计还有进一步改善的可能,接下来将继续采用一些其他的设计结构来改善此设计。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)