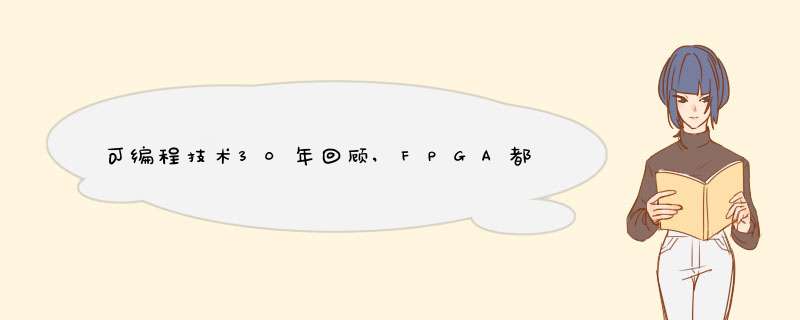

自引入以来,现场可编程门阵列(FPGA)的容量增加了10000倍以上, 性能增加了100倍. 单位功能的成本和功耗都减少了超过1000倍. 这些进步是由工艺缩放技术所推动的, 但是 FPGA 的故事比简单缩放技术的更复杂. 摩尔定律的数量效应推动了FPGA在体系结构、应用和方法方面发生质的变化. 因此, FPGA 已经经历了几个不同的发展阶段. 本文分别总结了发明、扩张、累积这三个阶段, 并讨论了它们的驱动压力和基本特征. 本文最后展望了未来的FPGA阶段.

Xilinx 在1984年引入了第一个现场可编程门阵列(FPGAs), 尽管直到Actel在1988年普及这个术语它们才被称为FPGAs. 在接下来的30年里,我们称之为FPGA的设备的容量增加了1万多倍,速度增加了100倍. 单位功能的成本和能耗降低了1000倍以上(见图1).

图1 Xilinx FPGA属性相对于1988年。容量指逻辑细胞计数。速度指可编程织物的同功能性能。价格指每个逻辑单元。能量指每个逻辑单元。价格和能量按一万倍放大。数据来源: Xilinx发表的数据。

这些进步在很大程度上是由工艺技术驱动的, 随半导体的扩展, 很容易把 FPGA 的进化看成是一个简单的容量发展. 这种看法太简单了。FPGA 进展的真实故事要有趣得多。

自其引入以来, FPGA 设备经过几个不同的发展阶段已取得进展. 每个阶段都受到工艺技术机会和应用程序需求的驱动。这些驱动压力引起设备特性和工具的可观察变化。在本文中, 我们回顾了FPGA的三阶段. 每个阶段长达8年, 并且每一段在回顾中都很明显。

三个阶段分别是:

1)发明阶段, 1984–1991;

2)扩张阶段, 1992–1999;

3)累积阶段, 2000–2007.

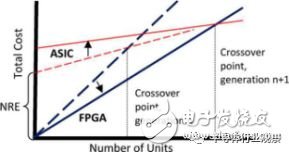

图2. FPGA与ASIC交叉点。 图表显示总成本与单位数量。 FPGA线条较暗,从左下角开始。 随着下一个工艺节点的采用(从较早节点的虚线箭头到稍后节点的实线箭头),由垂直虚线表示的交叉点变大。

二、前言: 关于FPGA的重大问题有哪些?

A.FPGA VS ASIC

20世纪80年代,专用集成电路(ASIC)公司为电子市场带来了一个惊人的产品:定制集成电路。 到20世纪80年代中期,有数十家公司在销售ASIC,在激烈的竞争中,成本低,容量大,速度快的技术更具受青睐。 当FPGA出现的时候,它在所有这几个方面上都并不突出,但却一枝独秀。这是为什么?

ASIC的功能是由自定义掩模工具决定的。ASIC的客户为这些掩模工具支付了前期的一次性工程(NRE)费用。由于没有定制的工具,FPGA降低了预付成本和建立定制数字逻辑的风险。通过制造一种可以被成百上千的客户使用的自定义硅设备,FPGA供应商可以有效地平摊所有客户的NRE成本,从而不会对任何一个客户收取任何费用,又同时增加了每个客户的单位芯片成本。

前期的NRE成本确保了FPGA在某些数量上比ASIC更具成本效益。FPGA供应商在他们的“交叉点”上吹嘘这个数字,这个数字证明了ASIC的更高的NRE开销。 在图2中,图线显示了购买数量单位的总成本。 ASIC具有NRE的初始成本,并且每个后续单元将其单位成本增加到总数。 FPGA没有NRE电荷,但是每个单元的成本都比功能相当的ASIC要高,因此斜率更陡峭。 两条线在交叉点相遇。 如果所需的单元数量少于此数量,则FPGA解决方案便宜; 超过该数量的单位表明ASIC具有较低的总体成本。

由于NRE成本占ASIC总体拥有成本的很大一部分,所以FPGA每单位成本超过ASIC成本的优势随着时间的推移而减少。 图2中的虚线表示某个工艺节点的总成本。 实线表示下一个工艺节点的情况,NRE成本增加,但是每个芯片的成本较低。 FPGA和ASIC都利用低成本制造,而ASIC NRE收费继续攀升,推高交叉点。 最终,交叉点变得如此之高,以至于大多数客户,单元的数量已经不再适用于ASIC。 定制芯片只保证非常高的性能或很高的体积; 所有其他人可以使用可编程解决方案。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)