本文针对全方位的信号路径系统中的高速全差分运放及高频宽14位模拟/数字转换器的随机及固定时钟抖动,具体分析、研究了超低噪声兼时钟抖动滤除技术。研究选用双级联PLLaTInum架构,配置高性能压控振荡器(VCXO),很好地实现了降噪和时钟抖动滤除的作用。

0 引言随着电子信息技术的发展,数据传输在军事航空、无线网络基础构建、测试与测量中发挥了巨大的作用。而时钟作为通信终端、发射与接收定量和同步标准,成为不可或缺的关键部分。信号传输过程中,晶振参考时钟本身具有较低的抖动,但由于IC、开关电源噪声、数据或时钟线的干扰引起的随机抖动和周期抖动(PJ)对时钟质量及系统性能都有比较大的影响。

典型的信号路径设计由信号传感器、模拟信号处理区块、数据转换器、接口及数字处理区块等多个不同环节组成,为了使系统充分发挥性能,路径所采用的主要元件必须符合有关要求。以模拟/数字转换器为例,系统设计工程师希望其信噪比(SNR)须不可低于60dB,因此14位的高频宽、频率要求高达1Gpsp的数据转换器被得以使用。在系统设计和使用的过程中,使用数据信号和参考时钟定位采样是重要环节,高精密时钟发生技术进而成为亟待发展的技术之一。通常情况下,设计所使用的单锁相环(PLL)式时钟发生器在工作过程中,乘法器会放大时钟抖动,同时引入其自身抖动,无法满足均值抖动指标Jrms《1ps@(12KHz~20MHz)的要求。

为了实现超低噪声精密时钟的发生,笔者对级联式PLL时钟抖动滤除技术做了研究和探讨,并对系统时钟抖动做和具体分析。

1.双级联PLL降噪滤抖设计当输入噪声较大时,系统具有较窄的环路带宽如几十Hz到几百Hz的情况下,借助本地高性能的压控振荡器,如VCXO、OCXO等,可以把参考时钟输入的噪声滤除干净,锁相环输出优越于参考时钟抖动性能的时钟信号。

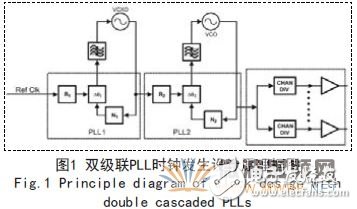

如图1所示,时钟发生采用了级联的双重PLL架构,以清除信号抖动,图中在VCO输出之后,续接了一个时钟分配电路。

第一个PLL采用了很窄的环路带宽,以便让外接的VCXO的频率锁定到输入的参考时钟信号上。极窄的环路带宽可以抑制参考时钟信号中的大部分相位噪声,使得VCXO的相位噪声成为主要的噪声分量。频率被锁定后的VCXO作为基准时钟输入第二个PLL,后者采用了较大的环路带宽,以便实现内置的VCO的锁定。这一较大的环路带宽意味着VCO的相位和频率都锁定到VCXO上,因此VCXO的噪声成为主要分量。

对于高于环路带宽的信号相位噪声,内部的VCO的相位噪声和输出分频器与驱动器将决定输出信号的相位噪声。

式(1)表明,总的噪声是基准时钟噪声、PLL噪声和VCO噪声的加权和:

加权函数H(f)是低通闭环传递函数,其中包含了电荷泵增益、环路滤波器响应、VCO增益和反馈通路(N)计数器等参数。该式表示了图1所示的每一级PLL的输出端的噪声模型。基准时钟信号噪声的增益(GREF)以及PLL噪声的增益(GPLL)也是具体的环路参数的函数。这里我们并不对这些增益和闭环响应H(f)的表达式进行推导,作为结论讨论。一般来说,构成H(f)的合成器件的诸多参数以及在式中所给出的增益值都可以由设计者来调整,其选择的标准是让合成器的输出端的总噪声(STOTAL(f))最小化。在这种情况下,最小化意味着合成后的总噪声的最小化。当对PLL2使用该噪声方程时,SREF(f)代表VCXO的噪声。SPLL(f)和SVCO(f)是由器件的特性所决定的,但SREF(f)取决于设计者所选用的VCXO.

2.技术分析与仿真2.1 相噪分析

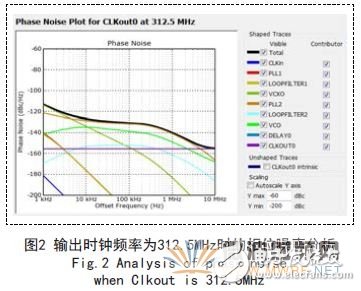

笔者的实验及仿真参数选取如下,PLL1:

125MHz的普通晶体参考输入,R=120,N=120,100uA的电荷汞电流;PLL2:NBXHGA019 125MHz的参考晶振输入,R=2,N=10,内部VCO分频设置为2,环路带宽以366kHz,相位余量为85.5度的4阶环路滤波,3.2mA的电荷汞电流;输出方式为LVPECL,同步输出分频选择各有不同,在2~510之间做随机选择。

图2是输出时钟频率为312.5MHz的相位噪声分析。相噪由参考输入的V C X O噪声、PLL开闭环噪声、内部VCO噪声共同决定。图中表明,总的相噪在1.000kHz处的相位偏移为-113.09dB/Hz,100.000kHz处-128.46dB/Hz,10,000.000kHz处-155.22dB/Hz.

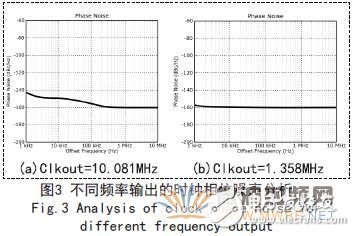

如图3所示为输出时钟频率分别为10.081MHz和1.358MHz时的时钟相位噪声分析图,由三者比较可知,随着输出频率的增加,相位噪声逐渐减小,使传输过程中的信噪比降低至系统所需60dB以下,满足设计需要。

2.2 RMS抖动特性

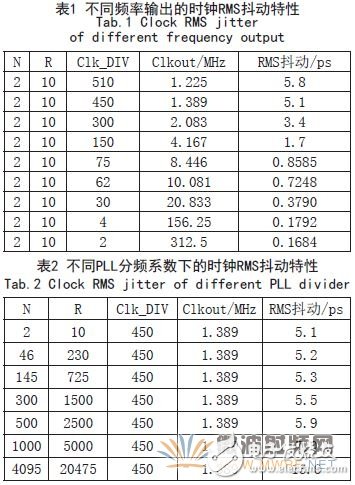

均值(RMS)抖动是表征时钟抖动的重要参数。如表1所示,为笔者在采样点数为1001,最低1kHz和最高10MHz的抖动探测中获取的不同频率输出下的RMS抖动情况。在PLL分频系数不变的情况下,测量得到的RMS抖动随着频率的增加逐渐减小,当频率为312.5MHz时,抖动为168.4fs,而用与提供基准的参考时钟的0.5pf相比有了极大的提高与改进。表2为不同分频系数下输出时钟RMS抖动情况,可以很明显得看到抖动随系数的增加在呈现指数的增长。

由仿真和研究可知,双级联PLL架构时钟发生设计,在实现抖动滤除低于300fs的同时,亦可实现多路频率合成及极低相位噪声(RMS抖动低至1.8ps@10KHz~5MHz)。超低抖动、低功耗的时钟发生技术满足了信号路径设计的模数转换采样及时钟和信号保证条件,同时,此类设计也可以被应用于无线基站、微波通信和100GE数据通信领域等。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)