随着 SoC 芯片性能的提高,各模块间的数据交换成为提高微处理器系统运行速度的瓶颈。DMA 控制器能够有效替代微处理器的加载/存储指令,显著提高系统的并行能力。传统的 DMA 的结构专用性强而可扩展性不足[1~3]。在高速并行系统中,单时钟域的设计已不能有效控制功耗的增长。面对 SoC 不断扩大的规模,还必须设计一种动态配置 DMA 通道的结构以提高逻辑资源的利用率。本文介绍了在 0.18um 工艺下,面向完整的 AMBA 总线结构的高性能 32 位 DMA 控制器的 ASIC 实现,提出了使用双时钟域配合具有同步复位的门控时钟(Gated Clock)实现功耗控制的方法。握手信号路由阵列的设计使得有限数量的通道可以匹配更多的总线外设。

VLSI是超大规模集成电路(Very Large Scale IntegraTIon)的简称,指几毫米见方的硅片上集成上万至百万晶体管、线宽在1微米以下的集成电路。由于晶体管与连线一次完成,故制作几个至上百万晶体管的工时和费用是等同的。大量生产时,硬件费用几乎可不计,而取决于设计费用。

超大规模集成电路是70年代后期研制成功的,主要用于制造存储器和微处理机。64k位随机存取存储器是第一代超大规模集成电路,大约包含15万个元件,线宽为3微米。目前超大规模集成电路的集成度已达到600万个晶体管,线宽达到0.3微米。用超大规模集成电路制造的电子设备,体积小、重量轻、功耗低、可靠性高。利用超大规模集成电路技术可以将一个电子分系统乃至整个电子系统“集成”在一块芯片上,完成信息采集、处理、存储等多种功能。例如,可以将整个386微处理机电路集成在一块芯片上,集成度达250万个晶体管。超大规模集成电路研制成功,是微电子技术的一次飞跃,大大推动了电子技术的进步,从而带动了军事技术和民用技术的发展。超大规模集成电路已成为衡量一个国家科学技术和工业发展水平的重要标志。也是世界主要工业国家,特别是美国和日本竞争最激烈的一个领域。超大规模集成电路将继续得到发展。

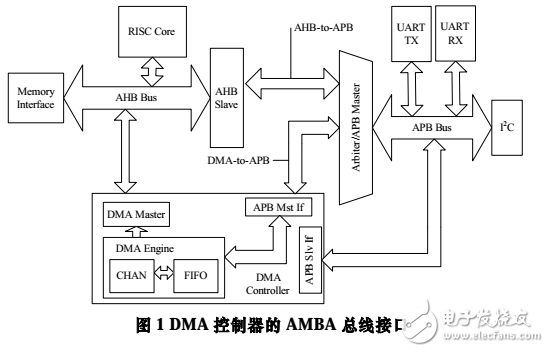

DMA 结构的比较AMBA是 ARM 公司提出的用于微处理器片上通信的先进的总线结构。一种典型的 AMBA 总线由 AHB 和 APB 总线分段构成。总线上的设备可以分为能够主动读写的主设备(Master)与只能接收来自 Master 请求的从设备(Slave)。

近来针对 DMA 控制器的研究引出了新的 SoC 架构,如使用分布式 Flyby DMA 结构[1];为数据吞吐量大的模块预设专用通道[2,3]等。这些结构的共同点在于数据在搬移过程中不需要经过缓存就可以达到指定地址。然而缺乏缓存结构的 DMA 有一定的局限性。从应用的角度来讲,在音视频编解码程序中普遍存在同端口内存数据块搬移的 *** 作,而非缓存结构的 DMA 无法在同端口上实现单周期的先读后写 *** 作。此外,在 APB 总线上只能存在一个 Master 设备,所以既无法为每个外设配置独立 Master 以获取数据,也不可能在低速总线上完成单周期传输。从功耗的角度看,当系统中存在较多 Master 模块时,总线仲裁器的负担就被加重,而仲裁器正是AMBA 总线功耗的主要来源。使用缓存结构的系统级 DMA 尽管存在数据传输的延时,但能适用于 AMBA 不同速度的分段总线,可扩展性远高于非缓存结构 DMA。

如图 1 所示,本文提出的 DMA 控制器在整个系统中可分为 3 个部分。DMA Master 端解析来自当前通道的命令包并发出 AHB 总线请求,完成缓存区与 AHB 总线的数据交换。 DMA 的引擎(DMA Engine)包含各个通道的逻辑资源与双口缓存结构(Dual Port FIFO)及相应的控制逻辑。DMA 控制器的 APB Master 发出 APB 的总线请求,这些信号与来自 AHB 的转换信号一起在两段总线的桥接(Bridge)部分进行仲裁选择,实现 APB 总线与 DMA 缓存区的数据交换。

DMA 的时钟域

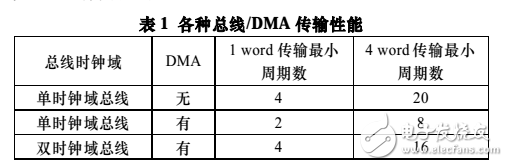

在不具备 DMA 的 AMBA 总线中,APB 唯一的 Master

在 AHB 总线的驱动下进行数据传输。两段总线以串行的方式工作。从表 1 中可知,由于在 AMBA 结构中微处理器不提供对 APB 的 Burst *** 作,完成对 APB 的 4 个 Word 的传输,至少需要 20 个 AHB 的时钟周期。而当存在 DMA 控制器时, APB 总线能缓存需要和 AHB 交换的数据,并且可以独立地驱动数据传输。不仅使传输周期减少了 50%,而且实现了 APB与AHB 的并行运行。

由于并行的实现,APB 总线上某些时间段中数据传输更加频繁。DMA 的 APB 信号进入总线以前必须经过仲裁,当使用类似于高速总线上的 Burst 模式时,APB 可以多个连续两周期的传输来运行,这增加了互连线的翻转频率。尤其在 DMA 多个通道相互交替占有 APB 时,这种翻转间隔便被缩小。因此,依据功耗 P = CV 2 f ,AHB 总线的二分频时钟被用来驱动 APB 总线。在这种配置下,相对于使用指令集进行的传输依然持有速度上的优势。

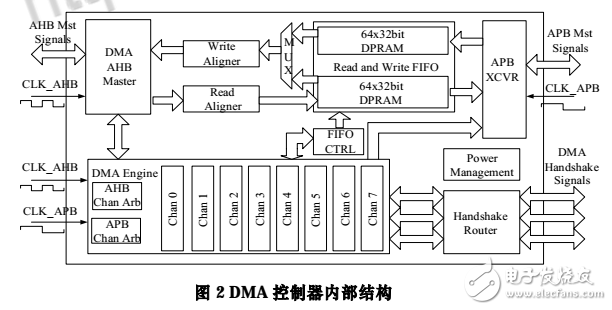

DMA 的内部结构DMA 控制器的核心部分围绕通道状态机和双口缓存数据的 FIFO 结构来设计。如图 2 所示,功能模块包括非整字地址对齐逻辑(Read/Write Aligner)、64×32bit 双口 FIFO、FIFO 控制逻辑、DMA 引擎、DMA 握手信号路由器(HandshakeRouter)和功耗管理电路。其中 DMA 引擎又包括 DMA 通道状态机逻辑和通道仲裁器(Chan Arb)。

双时钟域设计的难点在于时钟域的划分以及不同时钟的相位要求。从图 2 中可以看到,DMA 的数据通路部分由 2 个总线接口及 2 块 64×32bit 的双口 SRAM 组成,其中 DMA Master 接口与数据对齐逻辑由 CLK_AHB 来驱动,而 APB 端由 CLK_APB 来驱动。DMA 的通道根据数据流方向共分为两种:一种控制 AHB 上模块的数据交换;另一种控制 AHB 与 APB 上模块的数据交换。

为了减小面积,利用 APB 时钟是 AHB 时钟二分频的特点,将两种不同类型的通道复用同一个存储端口。这样,两种通道的状态机逻辑中使用各自的时钟产生 SRAM 读写地址与控制信号。为了支持多通道独立读写 *** 作以提高并行度,每个 AHB 与 APB 交换数据的通道必须使用读写独立的SRAM。这样,使用 2 块双口 SRAM 实现了不同时钟域缓存共享。每个通道拥有 2 块 8×32bit 的不同流向的缓存容量,以匹配 DMA 的 AHB Master 端最高支持 4 个 Word 的 Burst *** 作。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)