首先要知道自己在干什么?数字电路(fpga/asic)设计就是逻辑电路的实现,这样子说太窄了,因为asic还有不少是模拟的,呵呵。我们这里只讨论数字电路设计。实际上就是如何把我们从课堂上学到的逻辑电路使用原理图(很少有人用这个拉),或者硬件描述语言(Verilog/VHDL)来实现,或许你觉得这太简单了,其实再复杂的设计也就是用逻辑门电路搭起来的。你学习逻辑电路的时候或许会为卡拉图,触发器状态推倒公式而感到迷惑,但是其实有一点可以放心的是,实际设计中只要求你懂得接口时序和功能就可以了,用不着那么复杂得推倒公式,只要你能够用语言把逻辑关系表述清楚就可以了,具体这个逻辑关系采用什么门电路搭的,可以不关心,综合工具(synthesis tool)可以帮你处理。当然你要知道基本门电路的功能,比如D触发器,与门,非门,或门等的功能(不说多的,两输入的还是比较简单的)。---一句话,采用verilog或者VHDL描述设计对象的逻辑功能,这就是数字电路设计的任务!

说到这里入门必须要两个基本功:逻辑电路基础,硬件描述语言。有了这两个基本功,就算你其他都不会也能找到工作,呵呵,或许你会说,现在面试要问fpga,要问时序分析,有那么简单么?其实这些东西在你有了这两个基本功之后,其他的都可以慢慢学习。注意硬件描述语言和逻辑电路的学习可以同步学习,而且要牢记,学习硬件描述语言进步取决于你对电路的理解和你对仿真器的使用。为什么这样子说呢?因为硬件描述语言RTL(寄存器传输级)主要是用来给综合工具综合成电路的,所以要满足特定的coding style,这些coding style将对应这特定的逻辑,比如时序电路应该怎么写,组合电路怎么写,这是有一定约束的,为此若你对逻辑电路比较熟悉,你就知道自己写代码大体综合后会采用什么门电路来组成;另外,写代码就要仿真,这是不可以避免的---不仿真,你怎么知道自己写的代码符合设计的要求呢?能够熟练使用仿真器,你就有了调试代码的基本能力,否则,写再多的代码也没有用。这也是今天我感到兴奋的一个因素,目前正在使用vera验证语言,采用类C++++的风格,对于习惯 verilog的我开始还不习惯高级语言的调试环境,定位一个问题得花上一天;但是一旦你能够熟练使用编译仿真工具之后,你就会发现其实自己的很多想法可以很快的写成代码,并通过调试来提高自己对语言的理解。----学习的进步在于,把自己的想法用语言来实现,并调试验证是否正确。

学习fpga应该从xilinx和altera器件的入手,这是当今世界最大的两家可编程器件供应商,当然学习fpga应该你具备一定的Verilog的基础。我们就用xilinx作为例子来讲解吧。

fpga的开发流程,首先是综合,布局布线,生成bit文件,最后下载。

综合,可以用synplify,也可以用synopsys的fpga compiler,当然也可以用ISE自带的综合工具,Mentor也提供fpga开发的工具。作为入门,synplify是一个很好的选择,第一,可以熟悉电路结构,第二,作为入门你可以在synplify的综合流程中检查自己代码的质量。以前没有用LEDA做代码QA的时候,我是经常用 synplify作为QA的工具的,当然你得对synplify的综合策略和综合报告比较熟悉才行。综合完毕之后生成EDIF文件。

作为xilinx,第三方的综合工具可以提供EDIF或者NCF文件,自带的XST综合工具输出的是NGC,与此同时,我们可能还会用到xilinx的 core,core文件主要以edn形式存在;有了这些文件我们就进入implementaTIon阶段,这个阶段分translate,Map,PAR 三大部分,translate是把综合得到网表和core的网表文件转化为NGD文件,作为Map的输入,Map是把网表文件映射到Xilinx中的基本元件中,如slice,blockram等等,最后PAR也就是place and route,最后就可以生成bit文件了。推荐的书籍《FPGA/CPLD设计工具——Xilinx ISE5.x使用详解》,该书对整个设计流程有详细的描述,还介绍了很多高级技巧,不过对于asic设计人员,除非要做FPGA验证,否则没有必要看这些东西,因为学习FPGA就是一个完整的ASIC设计流程,不像做ASIC那样设计人员还分前端后端,做FPGA涉及的将会是很多因素,包括内部结构和板级的调试等等。

学习fpga除了学习开发流程之外,另外一方面是学习其内部结构。xilinx的fpga的结构介绍如下:基本单元是LUT,由LUT组成SLICE,由 SLICE组成CLB,具体多少个LUT组成SLICE,多少个SLICE组成CLB由不同的器件类型决定,可以参考datasheet。此外,就是 Block Ram,DLL或者是DCM,还有DSP等。现在流行SOC,不少高端器件还嵌入了微处理器,有软核有硬核。学习硬件结构最好的入门书籍是孟宪元先生的书,虽然时间有点久了,不过从我看的书来看,只有他才是分析得最为彻底的。现在介绍这方面的书籍也多了,不过,有点要提醒的,用什么器件看什么器件的 datasheet,没有必要把这个东西当教科书学,查一查就可以了。

学习fpga有机会买个板子自己写点程序跑一跑,应该是一件挺不错的事情。现在很多宽带通信应用的fpga设计有Serdes接口,DDR接口之类的,不是特殊要求,自己玩,估计也用不上那么复杂的,写几个状态机或者是UART就可以。

上回我们讨论了学习逻辑电路和硬件描述语言的方法。如何买书,如何看书。这回我们讨论fpga和asic设计有什么区别。

fpga现场可编程器件,PLD方面的东西,通过verilog编译成配置文件,加载到fpga中实现特定的功能。其实fpga本身就是一个芯片,只是你可以通过编程的方式修改内部逻辑连接和配置实现自己想要的功能。

asic专用集成芯片,是针对特定应用设计的芯片。实现asic,就如从一张白纸开始,你得有代码,之后综合,之后布局,布线,得到GDSII后去流片。fpga器件也是通过这个流程过来的,不过他应该算一个通用器件,就如cpu,可以在很多情况下应用,不像mp3芯片,它就只能播放mp3,所以只能称为专用芯片。不论通用还是专用,都有差不多的流程,注意上面说的是半定制的数字集成芯片的流程。作为模拟,还有一些特殊的全定制芯片,一般都是从版图开始的。

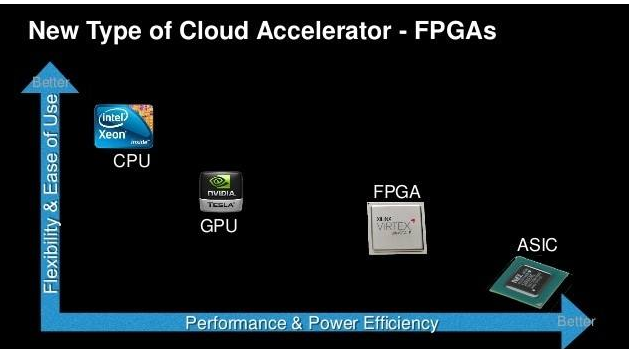

速度:相同的工艺和设计,在fpga上的速度应该比asic跑得慢。为什么呢?因为fpga内部是基于通用的结构,也就是LUT(look up table),它可以实现加法器,组合逻辑等等,而asic,一般你加法器就是加法器,而比较器就是比较器,fpga结构上的通用性必然导致冗余;另外,作为fpga基本单元是LUT(LUT组成SLICE,SLICE组成CLB--这是xilinx的结构),为此大的设计假如一个LUT实现不了,就得用两个LUT,一个SLICE实现不了就要用CLB,不同结构处于特定的位置,信号之间的互联,导致的wire delay是不可忽略的一部分。而对于asic来说没有结构上的限制,而且对于特定的实际可以在空间上靠得很近,相对之下wire delay和cell delay都应该比fpga小。当然LUT中也有DFF,作为高速的设计一般都会在一个简单的组合逻辑 *** 作之后打一拍,再做下一步的处理。

面积:从上面上看,fpga相对于asic来说还是大很多的。要是你知道自己的手机基带芯片是一个fpga做的,你肯定会气死。n大一个fpga,想让你放到口袋里面估计还是有困难。

功耗:也是明显的东西,fpga功耗比asic要大。

以上都是基于相同制造工艺和设计的条件下比较的。从另外一个侧面看,也就是开发速度和流程上看,fpga开发简单,asic开发流程长风险大。

fpga除了代码之外,从综合到布局布线生成配置文件都是通过软件自动产生的,当然可以有一定的约束。但是,你要知道,你只是在一个房子里面画画,这个房子就是现成的fpga。画得不满意,你搽掉,再画一个。不会对房子有多大影响-只要你不把fpga烧掉。

asic设计,你不仅要关心代码,而且你要关心时序,关心设计符合DFT的要求,关心layout,关心SI。。。。。。就相当于你什么都没有,现在房子要由你来盖,盖多大(floorplan),要如何盖,电源线如何走,水管如何设计,门开在那个方向等等的东西。一旦房子盖好了,你觉得不满意?你就得拆掉,某一个缺陷都影响这个房子。你想画画,可以,你得画得好,画不好就不能改了。因为asic不是可编程的fpga,内部结构一旦流片后就确定下来了。 bugs是asic中致命的东西!

对于费用来说,fpga贵在单片,开发工具和风险基本不存在。对于asic贵在流片的费用和开发工具,NRE费用随着工艺的提高变相当贵,除非你的芯片一次成功可以量产,否则单片费用将其贵无比!你想想留一次片50W,给你拿回来100颗样片,都是bugs。一片多少钱啊??!!

开发周期,fpga6个月,asic一年。若是一个设计人员说自己一年之内tapout了4-5个片子,估计他也只是做做综合或者后端。从设计到验证结束是一段漫长的时间,一旦验证初步完成,RTL2GDSII的过程是很快的。

asic设计入门(前端)

asic设计前后端是如何分的呢?asic设计的前后端就如FPGA设计的ImplementaTIon之前之后(Xilinx)的区分,前端负责综合网表之前的所有事情,而后端负责Netlist到GDSII的过程。注意这也不是绝对的,现在前端也可以用Physical Compiler做一些后端做的事情(物理综合),随殴ひ盏姆⒄梗昂蠖说姆纸庀咴嚼丛侥:恕5比籄SIC的前端还考虑到很多关于Power,DFT等等方面因素;后端呢,在这里粗略介绍一下,Floorplan,版图规划,主要指Macro的放置还有PG ring等的规划;Place-布局,主要指standard cell的放置;Route,布线;其中还涉及到DFT,DRC,LVS还有STA。这些东西了解一下就可以了。

ASIC前端设计入门,这个流程幸好没有忘记。不像FPGA那样(和器件关系太多),数字前端都应该是一样的。

1 系统规划需求分析----制定SpecificaTIon

2 模块划分-----根据SecificaTIon,开始划分模块,具体到接口时序和功能,最后书写详细设计文档。

3 模块编码输入----注意符合Coding Style

4 模块级仿真验证---行覆盖率应该达到99%(default语句是覆盖不到的)

5 系统集成和系统仿真验证----验证平台应该在Specification确定之后和代码编写并行进行。

6 综合----得到网表

7 STA-----验证时序

8 形式验证--验证网表和RTL的等效性

若是Netlist2GDSII的话这些就应该可以了,象DFT之类的估计后端人员都可以帮助你实现。看起来挺简单的,其实花时间最多的还是在前面,也就是综合之前的步骤是最费时间的,包括制定Specification,模块级的详细设计方案还有验证,一旦得到一个goden RTL,从RTL到GDSII是很快的。所谓garbage in garbage out,到了综合之后的步骤基本上不是对功能的修改,而是按照特定功能的实现,所以一个好的RTL是非常重要的。

在系统规划方面,复位,时钟方案是最重要的因素,其次是DFT;在模块编码的时候就是要注意这些要求了,比如不要内部私自生成时钟和复位信号,防止出现不必要的latch等等。模块级验证应该是系统验证关键部分,原来我们做TDSCDMA手机终端芯片的时候,Viterbi验证的是好几个步骤组成的,在模块级就验证做得非常完善,后来系统验证,FPGA验证到最后tapout回来都没有问题。当然大家都关心综合如何处理,STA如何处理,形式验证如何实现,因为这几个步骤不是所有人都可以接触的,毕竟这些工具都价格不菲;一个公司可以随便找几个人一起开发FPGA,但是说要随便找几个人做ASIC,估计 Tool的费用就要砸掉好几百W--这里指的是商用软件,假如你说其实D版的也可以用,^_^ 那就算你用了,流片的费用也不少啊。

下面我就一部分一部分给大家介绍asic前端设计的各个部分。

在没有介绍综合之后的流程之前,我先介绍一下从系统规划到综合前的流程,前面FPGA和这里的ASIC在这方面介绍的都不多,在这里补过,希望对大家有帮助。 系统规划当然是系统人员制定的,假如你想知道如何制定,大体上是系统功能,性能,系统接口,系统的时钟方案,复位方案,DFT方案;系统采用了多少 Memory,是否使用DSP,MCU,架构如何,最后die size和power大约多大等等;作为一名设计人员多数你会分到一个模块的设计,一般情况下在系统方案制定好之后就是模块划分了,很多情况下是根据功能来划分;模块划分之后,设计人员会不断讨论实现方案和关键问题的解决方法,开始是模块之间的接口,接着是模块内部的实现方案和时序,经过详细的讨论之后,这些都要写成详细设计方案。三年前自己的第一个设计是画了几个图就做设计的,小小的一个东西,没有文档,看草图,做了一个月;在积累了经验之后,改变了开发流程,也是大公司采用的方法,先写详细设计方案,再写代码;你会发现可能详细方案花了1个月,代码半个月就可以写完了。因为思路理清楚了,写代码当然简单了,千万不要一边写代码,一遍写设计方案,到了最后,问题一个都没有解决,代码改来改去,还是不能用。

再之就是调试,现在很多公司都在服务器上写代码,网络连接速度很慢,更加不用说调试了。我原来的习惯,也是现在的习惯就是在本机做设计,第一书写快,第二仿真快,对于模块设计应该是设计完一个模块就调试一个模块,而不是等系统集成的时候再测试模块。所以仿真调试的速度很重要,而在服务器上用VCS调试小模块,还不如在本机上用Modelsim快。刚入新公司,做模拟设计,人家一个月要完成的设计,我用了两个星期,道理很简单,我有一个代码书写和调试的平台,十分钟内就可以把一个代码调试n次。当然这个环境也不是大家都有,都会用,这也是我三年积累下来的东西^_^

综合工具

第一节: 什么是综合呢?synthesis,台湾翻译为-合成,其作用就是将硬件描述语言的RTL级代码转变为门级网表。当然,现在综合技术已经很成熟了,还有推出的行为(behavioral)综合和物理(physical)综合。我们这里讨论的是逻辑(logic)综合。

综合技术是提高设计产能的一个很重要的技术,没有综合技术的发展,我们就不可能用HDL实现电路的设计,因为HDL开始是用来供电路仿真建模使用的,到了后来才把其中一部分子集作为可综合的语言,也就是我们使用的RTL CODE。很多人入门都用HDL做设计,就以为HDL就只是用来做设计的,没有看到HDL最初始的一面,所以在验证的时候,就无法用好HDL另外一部分强大的功能。有时间还是可以看看Writing Testbench这本书,增强对HDL语言在验证方面作用的了解,也是提高对HDL认识很好的补充。

我们以DesignCompiler为例子讲解综合的过程。

首先,综合就要必须要用综合库,这个你可以向厂家要,综合库可以通过.lib这个库文件转变成.db综合库,这个过程可以在DesignCompiler 里面用实现,综合库里面有什么内容呢?.db 是无法阅读的,.lib是可以阅读的,里面有库的基本参数的单位,库运行的条件,各种参数,最重要的是两个部分,一个是WLM-Wire Load Model,一个Gate的定义(输入输出,功能,时序参数,面积等等);这只是StandarCell的库,另外还有其他库,如RAM,DSP的综合库,都以.db的形式存在。

综合需要三种输入,一个是代码,一个是综合库,一个是综合脚本script。综合脚本主要包括了一下内容,对综合工具环境的配置,对综合对象外部环境的设置(operation condiction),对WLD的设置,对综合对象的时序的约束,综合策略,综合优化,综合报告和输出。下面给入门的人一个现成的script例子。(tcl script)

####### Set Directary #########

set LIB typical

set SYNDIR $HOME

set SRCDIR $HOME/src

set SCRDIR $HOME/script

set RPTDIR $HOME/rpt

set SYNDB $HOME/db

set SYNOPSYS “/cad/synopsys/”

######Enviroment############

define_design_lib WORK -path $SYNDIR/WORK

set bus_naming_style %s_%d

set verilogout_single_bit “false”

set hdlin_enable_vpp “true”

set hdlin_enable_vpp “true”

set verilogout_no_tri “true”

set write_name_nets_same_as_ports “true”

set compile_preserve_sync_resets “true”

set ultra_optimization true

set verilogout_equation false

set verilogout_no_tri true

set sdc_write_unambiguous_names false

######Libary#################

set synopsys_path “$SYNOPSYS/libraries/syn \\

$SYNOPSYS/dw/sim_ver”

set standarcell_path “*”

set search_path “$search_path \\

$synopsys_path \\

$standarcell_path”

set target_library “typical.db”

set symbol_library “*”

set synthetic_library “dw_foundation.sldb”

set link_library “* $target_library dw_foundation.sldb”

######Read Design#############

analyze -format verilog -lib WORK [list *] 》 $RPTDIR/analyze.rpt

elaborate designtop -lib WORK -gate_clock 》 $RPTDIR/elaborate.rpt

write -format db -hier -modified -output $SYNDB/$TOPMODULE.rtl.db

current_design $TOPMODULE

#######Set INTERFACE ENV#########

set_drive 10 [all_inputs]

set_fanout_load 10 [all_outputs]

######Timing Exceptions#######

set_false_path -from rst_

uniquify

link

########Set Clock#############

create_clock -name CLK -p $PERIOD [get_ports clk] -waveform {0, 5}

set_clock_uncertainty 0.3 CLK

set_input_delay 3 -clock CLK [all_inputs]

set_output_delay 3 -clock CLK [all_outputs]

set_dont_touch clk

#######Compile Option############

compile -map_effort medium 》 $RPTDIR/compile.rpt

#######Report####################

report_timing 》 $RPTDIR/report_timing.rpt

report_area 》 $RPTDIR/area.rpt

#######Result####################

write -format db -hier -o $SYNDB/*.db

write -format verilog -hier -o $SYNDB/*.v

write_sdf -version 2.1 $SRCDIR/。。/netlist/*.sdf

write_constraints -cover_design -format sdf-v2.1 -output *.syn.sdf

write_script -hier -out $SCRDIR/*.sdc

这是一个非常完善的script 结构(仅供参考,这只是一个架构,具体语法可能还需补充和修正,不可随便使用在研发上,面得你花很多时间去调试脚本),使用于RTL2Netlist的综合,当然PAR之后的综合肯定不是这样子写的,其中原因建议大家看看《《advance chip synthesis》》。今后有空我再把script各个部分做详细见解,今天就写到这里。哎,写了那么多了,就是没有人捧场啊!^_^

########################################################################################################################

第二节,综合概述综合技术的研究可以追溯到20世纪60年代,IBM公司T.J.Watson研究中心开发 ALERT系统,将寄存器传输级算法描述转化成逻辑级的结构实现;20世纪70年代,综合技术发展迅速,但主要致力于较低层次的逻辑综合和版图综合;20 世纪80年代中期,专用集成电路的广泛应用,要求芯片设计大规模、高性能、短周期,大大推动了从算法级设计描速向寄存器传输级设计描述转换的高层次综合技术。

逻辑综合概念

逻辑综合负责将寄存器传输级的结构描述转化为逻辑层的结构描述,以及将逻辑层的结构描述转化为电路的结构描述。在数字IC设计领域常用的EDA综合工具中,最权威的要算Synopsys公司提供的综合工具。Synopsys公司提供的Design Compiler(DC)是业界流行的、功能强大的逻辑综合工具。用户只需要输入设计规格的HDL描述和时间约束,就可能得到较为优化的门级综合网表。此外,DC还集成了功能强大的静态时序分析引擎,并支持与后端布局布线工具交互工作。

逻辑综合的流程

从某种意义而言,综合就是将设计的HDL描速转化为门级网表的过程。Synopsys公司提供的综合工具DC把综合分为三个步骤进行:synthesis=translation+mapping+optimization。 Translation是指把设计的HDL描述转化为GTECH库元件组成的逻辑电路;GTECH库是Synopsys公司提供的通用的、独立于工艺的元件库。Mapping是指将GTECH库元件映射到某一特定的半导体工艺库上,此时的电路网表包含了相关的工艺参数。Optimization是根据设计者设定的时延、面积、线负载模型等综合约束条件对电路网表进一步优化的过程。从综合工具的使用流程来看,综合包括综合环境的设置,综合约束,综合优化,综合与后端流程等。

综合约束用来设定电路综合的目标,它包括设计环境约束、时间约束和面积约束。

设计环境约束指的是用来描述设计在工作时的温度、电压、驱动、负载等外部条件的一系列属性。基本的环境设置内容包括工作条件、负载模型、系统接口驱动或扇出能力等设置。这些属性约束在电路综合时是必须的,如果用户没有进行显示的说明,则DC在综合的时候会采用默认值。

时间约束内容包括定义时钟、定义时钟网络的时间约束和时序路径时间约束设定,以及非同步设计的时间约束等。了解延迟的计算是定义恰如其分的时间约束的关键。Synopsys公司支持几种延迟模型:一是CMOS通用的延迟模型,二是CMOS分段的线性延迟模型,三是非线性的查表延迟模型。深亚微米的设计,前两种模型并不常用,非线性的延迟模型以输入的迁越时间和输出电容负载为参变量计算延迟的时间值,其结果以表格的形式列出供DC查找。

面积约束和时间约束之间是一对矛盾且需要折中的关系,DC综合默认为时间约束比面积约束拥有更高的优先级。DC优化时默认不进行面积优化,如果你关注于芯片的面积,可以使用set_max_area命令设定面积的约束,使得DC完成时序约束之后继续进行面积优化。

在设定综合约束之后,一般并不马上进行综合优化。因为对于一个较大的设计来说,综合一次时间很长。因此,综合前确认综合约束命令是否正确添加到设计中时很有必要的,可以减少由于综合约束不正确重新综合优化的风险,减少综合反复的时间。检查综合约束设置的命令有report_design, report_port –verbose, report_clock [-skew], report_constraints, report_timimg_requirement等。

许多版图工具只接受Verilog或EDIF格式的综合网表作为输入。在综合后提供Verilog格式的网表送给后端的版图工具,IC工程师还必须对综合的网表做好一下处理:

1.彻底解决多次例化同一子模块的问题

2.修正设计中部分连线的命名以简化综合网表

3.删除整个设计中悬空的端口

4.确保每个实例化单元的引脚都是可见的

5.避免网表中存在assign语句、传输门和三态连线的定义

6.避免网表中存在不必要的门控时钟或门控复位信号

7.避免网表中引用的实例化名不存在对应的实现逻辑

在综合之后,我们还得对综合后的网表进行门级仿真,在门级仿真上Synopsys公司提供的VCS仿真工具在服务器上运行的速度是比较快的。门级仿真过程中还有一步就是带时序反标的时序仿真,通过DC或者PT写出SDF文件,在网表中将逻辑延迟和线延迟反标入电路中,模拟更加真实的情况。

功能仿真及验证

验证的目的视为了保证设计实现提供的功能特性是正确的,是与设计规范中定义的功能特性保持一致。验证的目的在于证明设计没有错误。然而事实上验证只能证明某些设计错误存在或者不存在,验证是一个穷举设计中可能存在的错误的过程。业界中存在着相当度的验证手段和验证的策略,其中主要的验证手段可以粗略地划分为功能仿真技术、静态时序分析技术、形式验证技术等。

功能仿真与调试

功能仿真是设计验证的主要形式。从仿真的抽象层次来看,包括基于事件(event based)的仿真,基于时钟周期(cycle based)的仿真,基于事务交易(tansaction based)的仿真。

基于事件的仿真器把输入激励的变化认为是事件的触发,每一个仿真时间仿真器处理一个事件触发,根据事件触发的内容对整个设计重新计算直到一个仿真稳态出现为止。

基于事件触发的仿真特点是同时覆盖了设计的功能和时序模型,仿真结果精确,它非常容易探测到设计中的毛刺电路,尤其适用于异步电路的仿真。

基于时钟周期的仿真在一个时钟周期那没有时间的概念,它只在时钟的上升沿或下降沿进行触发,每一个时钟周期的时间对电路计算一次。

基于事务交易的仿真以数据包、图形、语音等对象作为直接的仿真激励而不在是添加到设计引脚的激励波形。

功能验证的方法主要有三种:黑盒法、白盒法和灰盒法。

架构测试环境在软件仿真过程称作“writing testbenches”。Testbench通常是指这样的代码,它对设计进行恰当的配置、产生测试激励盒有选择性地观察地响应。Testbench一般用硬件描述语言Verilog HDL或VHDL实现,也可以包含C语言或者C++语言产生地激励数据加上PLI,现在业界还有专门地验证语言Vera和Specman E。

今后有空再跟大家介绍一下Modelsim和VCS:)

静态时序分析静态时序分析简称STA(Static Timming Analysis),它提供了一种针对大规模门级电路进行时序验证的有效方法。它指需要更具电路网表的拓扑,就可以检查电路设计中所有路径的时序特性,测试电路的覆盖率理论上可以达到100%,从而保证时序验证的完备性;同时由于不需要测试向量,所以STA验证所需时间远小于门级仿真时间。但是,静态时序分析也有自己的弱点,它无法验证电路功能的正确性,所以这一点必须由RTL级的功能仿真来保证,门级网表功能的正确性可以用门级仿真技术,也可以用后面讲到的形式验证技术。值得注意的是,静态时序分析只能有效地验证同步时序的正确性,对于大部分设计重可能包含地异步电路的时序验证,则必须通过门级仿真来保证其时序的正确性。由此我们可以得出这样子的结论:静态时序分析和门级时序仿真是从不同的侧重点来分析电路以保证电路的时序正确,它们是相辅相成的。

Synopsys公司的Prime time时序分析的工具,对设计电路进行以下几种分析:

1.从主要的输入端口到电路中所有触发器

2.从触发器到触发器

3.从触发器到主要输出端口

4.从主要的输出端口到主要的输出端口

静态时序分析工具把整个设计电路打散成上述四种类型的时序路径,分析不同路径的时序信息,得到建立时间和保持时间的计算结果。当然还有另外几条路径:如gated clock,DFF复位端的,具体可以参见PrimeTime的手册。

STA入门比较好的文章,也是5life转载过来的http://techcenter.dicder.com/data/2006/0114/article_102.htm

形式验证形式验证是一种静态的验证手段,它根据电路静态地判断两个设计在功能上是否等价,常用来判断一个设计在修改前和修改后其功能是否保持一致。它运行时无需测试向量,但是必须有一个参照设计和一个待验证的设计。参照设计时设计者认为功能上完备无缺的设计,理论上它可以用高级语言如C,C++实现的,也可以是用集成电路的建模镅詓ystemC,或者验证语言vera或SpecmanE实现的;但是就实现而言,多数形式验证过程中参照设计就是我们的RTL设计,一般用verilog或VHDL实现的。

当RTL级功能仿真或FPGA验证结束后,传统的IC设计流程需要完成一下几次门级仿真:综合后门级仿真;DFT之后的门级仿真;布局布线之后的门级仿真等,如果设计很大或者电路很复杂,往往需要庞大的测试向量来验证设计的功能及时序是否正确,这就使得我们花费在门级仿真的时间随着电路规模的增直线上升。

形式验证在ASIC设计流程中犹如一个迭代算法,其最初的输入是RTL设计,每次比较,都将上一次比较后的设计(第n-1次)作为参照设计处理之后的结果(第n次)进行比较,之所以这么做,是基于以下考虑:

1.形式验证工具开始比较前,首先在两个设计中找到一一对应的比较点。

2.如果一个设计改动太大,改变前后的功能是完全一致的,但如果形式验证工具无法找到适合的比较点,也会认为这两个设计不等价

形式验证在ASIC设计流程中主要应用在以下几个方面:RTL-RTL的对比,RTL-GATE的对比,GATE-GATE的对比。采用形式验证进行 RTL与RTL的比较,可以在较短的时间内验证并保证代码修改的过程中没有引入功能性的错误;进行RTL与GATE的对比,是验证源代码与综合之后的门级网表是否等价,以保证综合过程中不会出现任何错误;进行GATE与GATE的对比,主要是发生在验证插入DFT后的电路网表在功能上是否一致;生成时钟树前后的电路网表在功能上是否一致;布局布线前后的电路网表在功能上是否一致等。

什么是DFT,为什么要做DFT。可测试性技术(Design For Testability-DFT)就是试图增加电路中信号的可控制性和可观测性,以便及时经济地测试芯片是否存在物理缺陷,使用户拿到良好的芯片。其中包括Ad Hoc技术和结构化设计技术。目前,任何高集成度IC设计系统都采用结构化设计技术,其中主要扫描技术和内建自测两种技术。一个电路的测试性问题应该包括两个方面:

1.由外部输入信号来控制电路中的各个节点的电平值,称为可控制性。

2.从外部输出端观测内部故障地难易程度,称为可观测性

扫描技术是指电路中的任一状态移进或移出的能力,其特点使测试数据的串行化。比较常使用的是全扫描技术和边界扫描技术。全扫描技术是将电路中的所有触发器用特殊设计的具有扫描功能的触发器代替,使其在测试时链接成一个或几个移位寄存器,这样,电路分成了可以进行分别测试的纯组合电路和移位寄存器,电路中的所有状态可以直接从原始输入和输出端得到控制和观察。这样子的电路将时序电路的测试生成简化成组合电路的测试生成,由于组合电路的测试生成算法目前已经比较完善,并且在测试自动化生成方面比时序电路的测试生成容易得多,因此大大降低了测试生成的难度。

对于存储器模块的测试一般由生产厂家提供专门的BIST电路,通过BIST电路可以方便地对存储单元地存取功能进行测试,所谓的BIST电路是指把测试电路做到IC里面,利用测试电路固有的能力自行执行一个测试存储器的程序。另外MBIST还可以解决RAM SHADOW的问题提高芯片的可测试性。

为什么要做DFT呢?因为我们的设计,也就是RTL到GDSII交出去的只是一个版图,最后芯片需要生产织造是在foundry做的,也就是厂家根据你提供的数据GDSII做成芯片。这个流程过程中可能出现缺陷,这个缺陷可能是物理存在的,也可能是设计当中的遗留问题导致的,另外一方面在封装的过程也可能出现缺陷。为了保证我们的芯片能够不存在物理上的缺陷,所以就要做DFT。也就是说,你交给foundry一个加法器的GDSII,他在做的过程和封装的时候都可能引入缺陷;拿到这个加法器芯片你怎么知道,里面的一个与门,厂家给你做的就是一个正常工作的与门呢?你怎么知道厂家做好的加法器的dier在封装之后引脚就能正常输入呢?一句话,就是通过DFT!如何做DFT呢,就是上面提到的拉。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)