低压CM0S带隙基准电压源设计

近年来,随着微电子技术的迅速发展,低压低功耗已成为当今电路设计的重要标准之一。比如,在一些使用电池的系统中,要求电源电压在3 V以下。因此,作为电源调节器、A/D和D/A转换器等电路核心功能模块之一的电压基准源,必然要求在低电源电压下工作。基准电压源广泛应用于电源调节器、A/D和D/A转换器、数据采集系统,以及各种测量设备中。

在传统的带隙基准源设计中,输出电压常在1.25 V左右,这就限制了最小电源电压。另一方面,共集电极的寄生BJT和运算放大器的共模输入电压,也限制了PTAT电流生成环路的低压设计。近年来,一些文献力图解决这方面的问题。归纳起来,前一问题可以通过合适的电阻分压来实现;第二个问题可以通过BiCMOS工艺来实现,或通过低阈值电压的MOS器件来实现,但工艺上的难度以及设计成本将上升。

基于上面的考虑,本文首先对传统的带隙电压源原理进行分析,然后提出了一种比较廉价且性能较高的低压带隙基准电压源,采用电流反馈、一级温度补偿技术设计了低压CMOS带隙基准源电路,使其电路能工作在较低的电压下。本文介绍这种带隙电压基准源的设计原理,给出了电路的仿真结果,并对结果进行了分析。并基于CSMC 0.5μm Double Poly Mix Process对电路进行了仿真,得到理想的结果。

低压COMS基准电压源设计

1.1 传统的带隙基准源

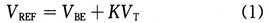

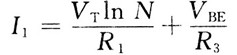

图1为带隙基准电压源的原理示意图。双极性晶体管的基极-发射极电压VBE,具有负的温度系数,其温度系数一般为-2.2 mV/K。而热电压VT具有正的温度系数,其温度系数在室温下为十0.085 V/K。将VT乘以常数K并和VBE相加就得到输出电压VREF:

将式(1)对温度T微分并代入VBE和VT的温度系数可求得K,它使VREF的温度系数在理论上为零。VBE受电源电压变化的影响很小,因而带隙基准电压的输出电压受电源的影响也很小。

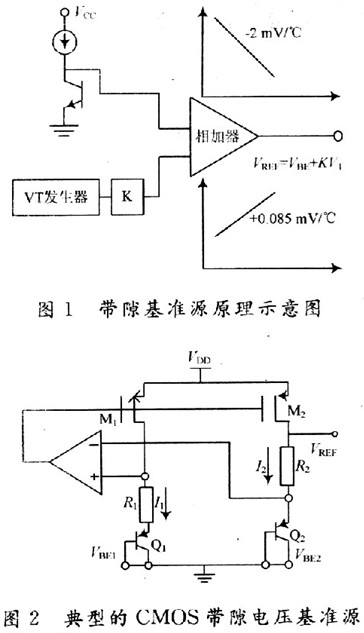

图2是典型的CMOS带隙电压基准源电路。两个PNP管Q1,Q2的基极一发射极电压差△VBE:

式中:J1和J2是流过Ql和Q2的电流密度。运算放大器的作用使电路处于深度负反馈状态,使得节点1和节点2的电压相等。即:

由图2可得:

通过M1和M2的镜像作用,使得I1和I2相等,结合式(4)和式(5)可得:

式中;A1和A2是Q1和Q2的发射极面积。比较式(5)和式(1),可得常数K为:

在实际设计中,K值即为式(7)表示。

传统带隙基准源结构能输出比较精确的电压,但其电源电压较高(大于3 V),且基准输出范围有限(1.2 V以上)。要在1.8 V以下的电源电压得到1.2 V以下的精确基准电压,就必须对基准源结构上进行改进和提高。

1.2 低压COMS基准电压源的电路设计

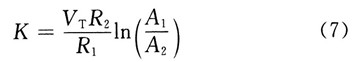

本设计基于CSMC-O.5μm-CMOS工艺(NMOS的阈值电压为0.536 V,PMOS的阈值电压为-0.736 V)。采用一级温度补偿、电流反馈技术设计的低压带隙基准源电路如图3所示。低压带隙基准源的电流不仅用于提供基准输出所需的电流,也用于产生差分放大器所需的电流源偏置电压,简化了电路和版图设计。

为了与CMOS标准工艺兼容,电路中PNP的e,b,c区分别采用P+,N-well,P-sub集电极接地。Q2和Q1的发射极面积比为8:1,流过Q1和Q2的电流相等,这样△VBE等于VTln 8。流过电阻R1的电流与热力学温度成正比。三路镜像电流源使得流过P2,P3,P4的电流相等(I1=I2=I3)。

输出电压VREF为:

电路中的温度补偿系数K为:

通过调节R4的值,可以调节输出电压VREF的大小。在电源电压变化时,P2,P3,P4的漏源电压值保持不变,与电源电压无关,其栅极电压由运放调节。为了降低电路的复杂度,应用电流反馈原理,运放采用简单的一阶运放,由于VDD的变化多于GND的变化,故运放的输入采用NMOS的差分对结构。因为整个电路在低压下工作,故整个电路设计的重点是要保证低压下运放的正常工作。

由于带隙基准源存在两个电路平衡点,即零点和正常工作点。当基准源工作在零点时,节点1、2的电压等于零,基准源没有电流产生。固需要设计一个启动电路,避免基准源工作在平衡零点。本设计的启动电路由N5、N6和P7构成。当电路工作在零点时,N6管导通,迅速提高节点1、2的电压,产生基准电流,节点1的电压通过P7和N5组成的反相器,使N6管完全截止,节点1、2的电压回落在稳定的工作点上,基准源开始正常工作。

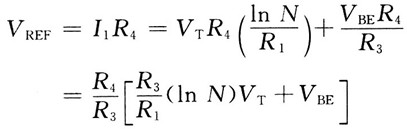

电路的器件参数如表1所示,P2,P3,P4管的尺寸较大,是为了降低电路中的1/f噪声。电流镜的负载管P5,P6和差分对管N1,N2的宽长比较大,以抑制电路的热噪声。由于电路中的电阻值较大,故在工艺中用阱电阻实现。电容C0有助于电路的稳定,同时还可以减小于运放的宽度,有助于降低噪声的影响。

2 仿真与结果分析

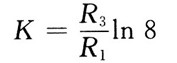

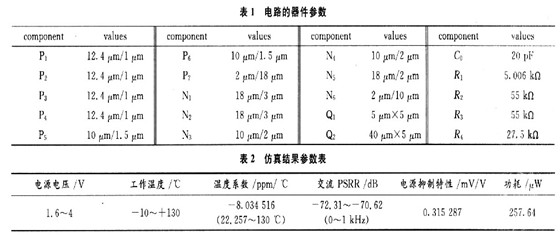

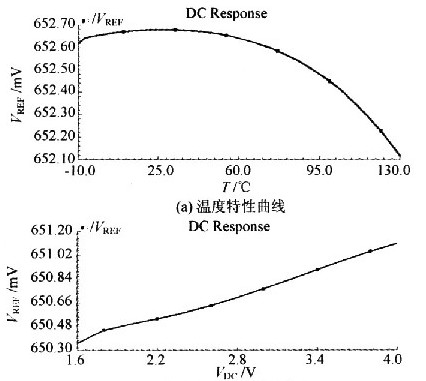

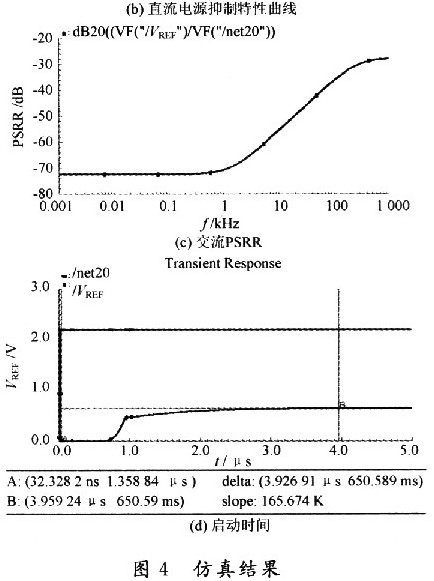

在Cadence设计平台下的Spectre仿真器中基于CSMC 0.5 μm CMOS工艺模型对电路进行了仿真。得到电路的温度特性曲线、直流电源抑制特性曲线、交流PSRR特性曲线、启动时间曲线如图4所示。各项仿真结果参数如表2所示。

3 结语

在应用典型CMOS电压基准源的基础上,综合一级温度补偿、电流补偿技术,设计了带隙电压基准源电路。该带隙基准源电路的电源工作范围为1.6~4 V,工作温度为-10~+130℃,基准输出电压VREF为(650.5±0.5)mV,温度系数可低至2.0 ppm/℃,电源抑制比为-70 dB。仿真结果证明了设计的正确性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)