本文介绍了ARM S3C4510B系统的异常中断机制,包括异常中断的分类,响应与返回;中断处理程序的安装与调用;SWI,IRQ中断的实例与关键代码。

随着人们对于电子产品的要求越来越高,以80C51系列为代表的8位处理器系统开始面临越来越多的局限和挑战,人们对于高性能芯片和嵌入式功能的呼声也越来越高。16/32 位的处理器系统得到了前所未有的关注和重视。32位ARM体系系列处理器便是其中的代表。S3C4510B处理器是基于ARM7体系16/32位RISC处理器,内部集成了8KB的CACHE/SDRAM,内嵌EARTHNET控制器,拥有7种处理器模式和内部多线程和外部多处理器的处理器结构。在嵌入式系统中具有重要意义的异常中断技术在S3C4510B系统中也体现了ARM体系独有的一些的特点。本文根据S3C4510B系统的特点,分析了该系统中七种异常中断的功能及特点。并给出了SWI异常中断(外部中断)和IRQ异常中断(软件中断)的应用实例代码。

1 S3C4510B系统中的异常中断

1.1 S3C4510B系统异常中断的特点

S3C4510B系统中控制程序执行流程的方式通常有三种,一是正常程序执行过程,即根据指令类型增加程序计数器PC使程序顺序执行;二是通过跳转的方式来控制程序的执行,可以利用跳转的命令执行跳转 *** 作,也可以通过直接修改程序计数器来达到跳转的目的;三是异常中断的方式,可以根据软件的执行情况,外部设备的异常请求等实现内部、外部异常的处理,系统功能的调用和程序进程的控制等功能。

S3C4510B系统的异常中断具有以下几个特点。首先,作为ARM体系RTOS(实时 *** 作系统)组成部分,程序中的异常中断必须按照ARM体系的要求进行处理器模式的转换。其次,如果对系统的优化有需求时,可以进行32位的ARM处理指令和16位的THUMB指令的转换。另外,S3C4510B处理器正常运行时,保存的返回地址是通过将PC存入LR寄存器完成的,由于中断产生时的计数器PC的值有时已经更新,如产生了外部中断和快速中断等;有时可能尚未更新,如软件中断和未定义指令中止等,故必须根据实际情况对返回地址进行软件修正之后才能正确返回。最后还要注意,ARM体系支持c语言和汇编语言程序的相互之间的调用,并有ATPCS规则进行协调,所以异常中断处理程序必需按照ATPCS规则进行寄存器处理。

1.2 S3C4510B系统中的异常中断的类型

S3C4510B拥有七种不同的异常中断类型,分别适应于不同的中断需要。根据ARM系列处理器的特点,各种异常中断对应于ARM系列的不同工作模式。其种类和对应关系如表1所示。

其中,复位中断是优先级最高的中断。在复位引脚有效的前提下,系统加电或系统复位时都会引起复位中断。数据访问中止是在数据访问指令的目标地址不存在或者该地址不允许当前指令访问的情况下产生的。指令预取中止中断是处理器或系统协处理器认为当前指令未定义,当系统预取该指令时,本中断执行。未定义中止在处理器或系统协处理器认为当前指令未定义时产生,故而可以根据该异常中断机制仿真浮点向量运算。快速中断和外部中断都是在对应的中断请求引脚有效,且状态寄存器中的相应中断禁止标志位清零时产生。其中的外部中断还可以用来进行各系统进程的切换;软中断由用户定义,在程序运行时由SWI指令调用,可用于用户模式下的程序调用特权模式指令。在RTOS系统中可以通过该中断机制实现系统功能调用。

1.3 S3C4510B系统对异常中断的响应

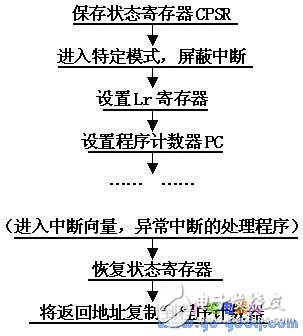

S3C4510B系统对异常中断的响应流程如下:

(1) 保存处理器当前状态寄存器CPSR的值、中断屏蔽以及各条件标志位到将要执行的异常中断的SPSR中。 电子电路图

(2) 设置当前程序状态寄存器CPSR的值。其中包括:设置CPSR相应位的值使处理器进入特定的处理器模式;按要求屏蔽中断,通常应该屏蔽IRQ中断,在FIQ中断时屏蔽FIQ中断。

(3) 设置Lr寄存器。将中断相应模式的Lr寄存器的值设置为异常中断的返回地址。

(4) 处理程序计数器PC。将PC值设为相应的中断向量的地址,从而实现跳转以执行中断程序。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)