双积分型A/D转换器ICL7107是一种间接A/D转换器。它通过对输入模拟电压和参考电压分别进行两次积分,将输入电压平均值变换成与之成正比的时间间隔,然后利用脉冲时间间隔,进而得出相应的数字性输出。

它包括积分器、比较器、计数器,控制逻辑和时钟信号源。积分器是A/D转换器的心脏,在一个测量周期内,积分器先后对输入信号电压和基准电压进行两次积分。比较器将积分器的输出信号与零电平进行比较,比较的结果作为数字电路的控制信一号。

时钟信号源的标准周期Tc 作为测量时间间隔的标准时间。它是由内部的两个反向器以及外部的RC组成的。

计数器对反向积分过程的时钟脉冲进行计数。控制逻辑包括分频器、译码器、相位驱动器、控制器和锁存器。分频器用来对时钟脉冲逐渐分频,得到所需的计数脉冲fc和共阳极LED数码管公共电极所需的方波信号fc。

(1) 31/2位双积分型A/D转换器ICL7107功能与特点

① ICL7107是31/2位双积分型A/D转换器,属于CMoS大规模集成电路,它的最大显示值为士1999,最小分辨率为100uV,转换精度为0.05士1 个字。

② 能直接驱动共阳极LED数码管,不需要另加驱动器件,使整机线路简化,采用士5V两组电源供电,并将第21脚的GND接第30脚的IN 。

③ 在芯片内部从V+与COM之间有一个稳定性很高的2.8V基准电源,通过电阻分压器可获得所需的基准电压VREF 。

④ 能通过内部的模拟开关实现自动调零和自动极性显示功能。 ⑤ 输入阻抗高,对输入信号无衰减作用。

⑥ 整机组装方便,无需外加有源器件,配上电阻、电容和LED共阳极数码管,就能构成一只直流数字电压表头。

⑦ 噪音低,温漂小,具有良好的可靠性,寿命长。 ⑧ 芯片本身功耗小于15mw(不包括LED)。

⑨ 不设有一专门的小数点驱动信号。使用时可将LED共阳极数数码管公共阳极接V+. ⑩ 可以方便的进行功能检查。

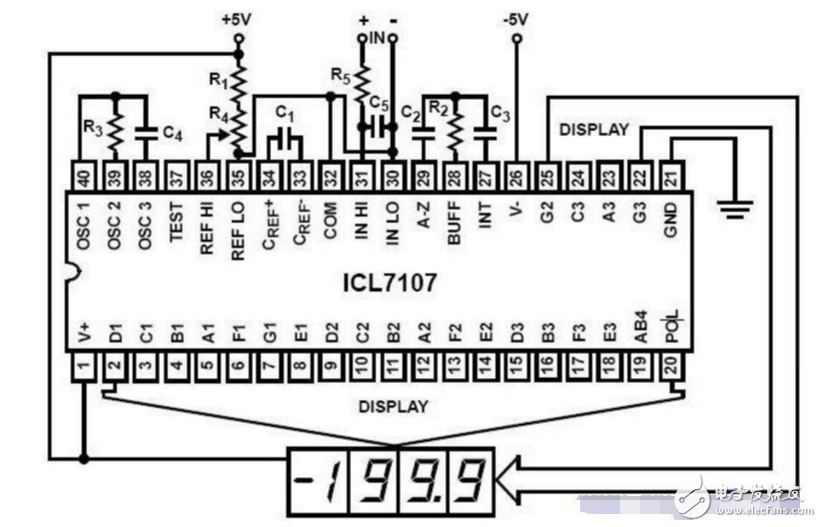

图1 ICL7107的引脚图及典型电路

(2) ICL7107引脚功能

au-gu,aT-gT,aH-gH:分别为个位、十位、百位笔画的驱动信号,依次接个位、十位、百位LED显示器的相应笔画电极。

Bck:千位笔画驱动信号。接千位LEO显示器的相应的笔画电极。 PM:液晶显示器背面公共电极的驱动端,简称背电极。

Oscl-OSc3 :时钟振荡器的引出端,外接阻容或石英晶体组成的振荡器。第38脚至第40脚电容量的选择是根据下列公式来决定: Fosl = 0.45/RC

COM :模拟信号公共端,简称“模拟地”,使 用时一般与输入信号的负端以及基准电压的负极相连。 TEST :测试端,该端经过500欧姆电阻接至逻辑电路的公共地,故也称“逻辑地”或“数字地”。 VREF+ VREF- :基准电压正负端。 CREF:外接基准电容端。

INT:27是一个积分电容器,必须选择温度系数小不致使积分器的输入电压产生漂移现象的元件 IN+和IN- :模拟量输入端,分别接输入信号的正端和负端。

AZ:积分器和比较器的反向输入端,接自动调零电容CAz 。如果应用在200mV满刻度的场合是使用0.47μF,而2V满刻度是0.047μF。

BUF:缓冲放大器输出端,接积分电阻Rint。其输出级的无功电流( idling current )是100μA,而缓冲器与积分器能够供给20μA的驱动电流,从此脚接一个Rint至积分电容器,其值在满刻度200mV时选用47K,而2V满刻度则使用470K。

ICL7107与8031接口的设计ICL7107 是Intersil 公司专为数字仪表而设计的3位半双斜积分A/D转换器。它只需少量的普通元件组成外围电路,就能做成精密的数字仪表,具有分辨力高和抗干扰能力强等特点,以其很高的性能价格比被广泛地采用。它能直接驱动LED数码块,但没有相应的BCD代码输出”,也没有A/D转换的状态标志输出,因而不能接入微机系统进行现场数据的采集和处理。本文提出了一一种极为简便的方法,使ICL7107实现了与80 31的接口,从而扩展了它的功能和使用范围。

接口条件的分析

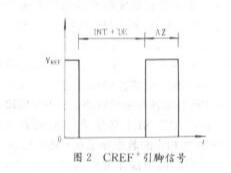

ICL7107的A/D转换周期分为三个阶段:积分INT)阶段、消除积分(DE)阶段和自动调零(AZ)阶段,如图1所示。

一个转换周期的时间为4000个计数脉冲周期,积分阶段是在规定的1000 个计数脉冲周期内对输人电压积分;消除积分阶段是对基准电压进行反向积分,同时由内部计数器计数,至积分输出为0,这段时间的计数值与输人电压成线性比例,其范围为0~2000余下的时间用于自动调零,在输人的电压为0~2000 范围内,自动调零时间就在3000- 1000 个计数脉冲周期的范围内变动。这个内部计数脉冲的频率是7107时钟振荡频率的4分频。

如果能够找到- 一个可以标志A/D转换周期的状态信号,用它作为接口的联络(handshake)信号,就有了实现接口的基础。根据1CL.71017的内部结构原理,在第34 号引脚(CREF‘ )可以找到如图2所示的信号波形。

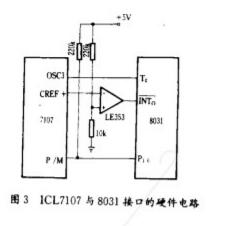

在INT 和DE的两个阶段内,这条引脚呈低电平在AZ阶段内,这条引脚的电平为基准电中。我们可将这个信号变换成与8031兼容的TTL电平。这样,就可用类同于文献的办法,画出如图3所示的接口硬件电路。

接口的设计与实现

图3的电路中,只用了8031的三根口线,To口设定为计数方式1J,INTo和P1.0分别接收经电平变换后的A/D转换状态信号和正负极性信号。用ICL710构成的数字仪表,现场输人信号的极性一般都已确定。因此P 。口线的连接往往可以省略。在程序中,设GATE=1,使INTo的作用为To的门控,在INTo=1期间To对7107的时钟脉冲计数,而在INTo=0时停止计数。设定外部中断0 为边沿触发.T 计数值的读取和处理安排于中断服务程序中。由于ICL7107的内部计数脉冲是它时钟周期的4分频,只要将T 的计数值除以4,再减去积分阶段固有的1000 个计数值,即得到A/D 转换的二进制结果。

参考程序如下:

本文实现的接口方法,是在ICL的片内定时积分和定斜率消除积分的计数过程中,由801的个定时,计数器对它的时钟脉冲计数,该计数值经分频处理并减去定时积分的固有计数值,即得3位半A/D转换器的二进制结果。710的内部计数值只供译码显示,而801定时,计数器读数而得的转换结果即为智能化仪表的现场数据。两者各尽所能,各司其职。由8031读取的转换结果与710驱动的LED显示结果严格- 一致。这种接口方法,对ICL 其它带显示驱动的A/D转换器,如7106.7116.7117.7126.7129 及7137等也同样适用。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)