曾几何时,使用xilinx器件的工程师都开始接触了Ultrafastdesign methodology 这个新名词。这个名词简称为UFDM,可以说是xilinx总结的关于FPGA设计方方面面的一种设计方法学。它其中的很多内容可能在于V6、V5那一代就提到过。比如xilinx器件关于复位信号的使用原则这一点,很早就提出了。UFDM有点类似我们都学习的“三个代表”这些,把FPGA设计的精髓、注意事项整理在一起,还有针对于软硬件设计的checklist,更加全面的帮助工程师减少debug的时间。

UFDM建议正确的HDL coding风格来满足目标器件,讨论时序约束和时序收敛。正确的IO约束,IO管脚分配和布局,物理约束,并提供了满足时序收敛的技巧和让FPGA工作快速稳定的方法。

在通信,医疗,航空和消费电子领域,FPGA的设计变得越来越复杂,不断增加器件的容量、设计的性能。在TIme to market的要求下,很多项目的设计周期都很短暂,如何在有限时间内,正确的实现设计需求是产品量产的关键。

Vivado中UFDM是所有使用xilinx器件的工程师的最佳经验的集合,覆盖了包括单板设计、IP创建、设计实现,时序技巧,硬件debug等内容。使用UFDM会指引工程师成功完成项目预期。

Xilinx建议设计者使用UFDM首先阅读ug949,这个文档包含很多PCB设计的细节,FPGA功耗评估检查,DRC检查的规则。遵循文档的内容,可以避免因不合理的布局引起的TIming收敛问题,节省debug时间。

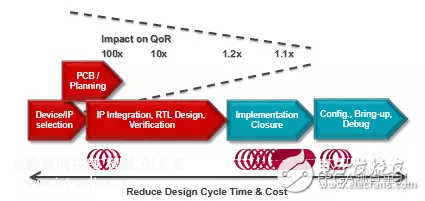

图1.Greaterimpact on QOR

图1是一张FPGA设计流程图,每个FPGA设计项目基本上都是器件选型、IO分配和PCB布局、RTL实现、综合布局布线和时序收敛、配置下载和调试几个阶段。在设计初期,当我们使用vivado做FPGA设计时,我们有很多选择,这些选择都能够直接影响到整个设计的性能。比如,我们可以选择基于C语言来完成设计,也可以通过HDL语言来描述设计,这都会极大地影响整个设计的质量。在整个设计流程,利用vivado UFDM工具不断产生时序报告和结果,不断修正XDC和源文件的代码,这样就会节省后面布局布线很多时间。

设计流程的后面几个阶段,对整个设计的性能影响都比较有限了,从100x 到1.1X。

另外UFDM也提到了coding需要和硬件结构相匹配的,很多设计代码仅考虑实现而不考虑FPGA的设计底层,这样在TIming上也很难收敛,尽量多使用BRAM、DSP slice等FPGA特有的资源。

希望UFDM能够对设计有所帮助,成为你设计的小助手!

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)