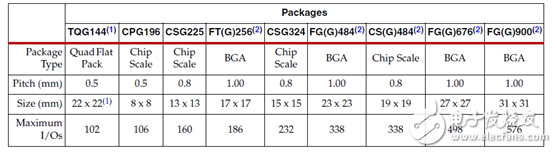

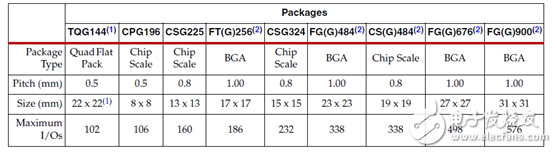

1. Spartan-6系列封装概述

Spartan-6系列具有低成本、省空间的封装形式,能使用户引脚密度最大化。所有Spartan-6 LX器件之间的引脚分配是兼容的,所有Spartan-6 LXT器件之间的引脚分配是兼容的,但是Spartan-6 LX和Spartan-6 LXT器件之间的引脚分配是不兼容的。

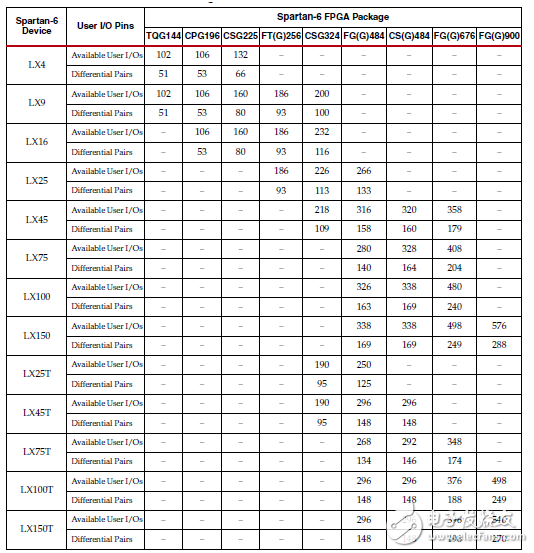

表1:Spartan-6系列FPGA封装

2. Spartan-6系列引脚分配及功能详述

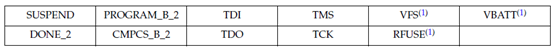

Spartan-6系列有自己的专用引脚,这些引脚是不能作为Select IO使用的,这些专用引脚包括:

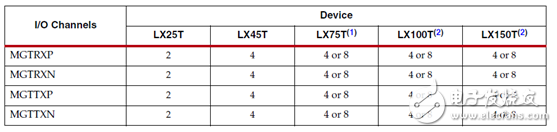

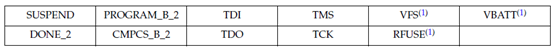

专用配置引脚,表格2所示,GTP高速串行收发器引脚,表格3所示

表2:Spartan-6 FPGA专用配置引脚

注意:只有LX75, LX75T, LX100, LX100T, LX150, and LX150T器件才有VFS、VBATT、RFUSE引脚。

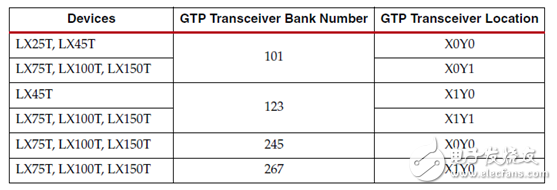

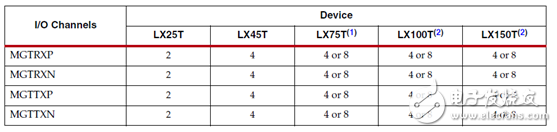

表3:Spartan-6器件GTP通道数目

注意:LX75T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676中封装了8个GTP通道;LX100T在FG(G)484 和 CS(G)484中封装4个GTP通道,而在FG(G)676 和 FG(G)900中封装了8个GTP通道。

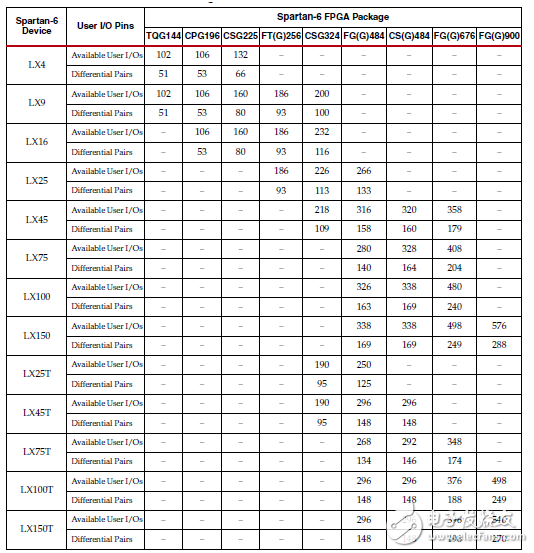

如表4,每一种型号、每一种封装的器件的可用IO引脚数目不尽相同,例如对于LX4 TQG144器件,它总共有引脚144个,其中可作为单端IO引脚使用的IO个数为102个,这102个单端引脚可作为51对差分IO使用,另外的32个引脚为电源或特殊功能如配置引脚。

表4:Spartan6系列各型号封装可用的IO资源汇总

表5:引脚功能详述

引脚名

方向

描述

IO_LXXY_#

Input/

Output

IO表示这是一个具有输入输出功能的引脚,XX表示该引脚在其Bank内的惟一标识,Y表示是差分引脚的P还是N引脚

MulTI-FuncTIon Pins

IO_LXXY_ZZZ_#

Zzz代表该引脚除IO功能之外的其他功能,

Dn

Input/

Output

(during readback)

在SelectMAP/BPI模式中,D0—D15是用于配置 *** 作的数据引脚,在从SelectMAP的回读阶段,当RDWR_B为低电平时,Dn为输出引脚,在配置过程结束后,该引脚可作为通用IO口使用

D0_DIN_MISO_MISO1

Input

在Bit-serial模式中,DIN是惟一的数据输入引脚;

在SPI模式中,MISO是主输入从输出引脚;

在SPI x2 or x4模式中,MISO1是SPI总线的第二根数据线;

D1_MISO2,

D2_MISO3

Input

在SelectMAP/BPI模式中,D1、D2是配置数据线的低2bit;在SPIx4 模式中,MISO2和MISO3是SPI总线的数据线的高2bit

An

Output

在BPI模式中A0—A25是输出地址线,配置完成后,它们可作为普通IO使用

AWAKE

Output

挂起模式中的状态输出引脚,如果没有使能挂起模式,该引脚可作为普通IO引脚

MOSI_CSI_B_MISO0

Input/

Output

在SPI配置模式中的主输出从输入引脚;

在SelectMAP模式中,CSI_B是低有效的Flash片选信号;

在SPI x2 or x4模式中,这是最低数据线

FCS_B

Output

在BPI模式中,BPI flash的片选信号

FOE_B

Output

在BPI模式中,BPI flash的输出使能

FWE_B

Output

在BPI模式中,BPI flash写使能

LDC

Output

在BPI模式中,在配置阶段LDC保持低电平

HDC

Output

在BPI模式中,在配置阶段HDC保持低电平

CSO_B

Output

在SelectMAP/BPI模式中,菊花链片选信号;

在SPI模式中,是SPI Flash的片选信号;

IRDY1/2,

TRDY1/2

Output

使用PCI 的IP Core时,它们作为IRDY和TRDY信号

DOUT_BUSY

Output

在SelectMAP模式中,BUSY表示设备状态;

在Bit-serial模式中,DOUT输出数据给菊花链下游的设备

RDWR_B_VREF

Input

在SelectMAP模式中,RDWR_B是低有效的写使能信号;配置完成后,可当做普通IO使用

HSWAPEN

Input

当是低电平时,在配置之前将所有IO上拉

INIT_B

BidirecTIonal

(open-drain)

低电平表示配置存储器是空的;当被拉低时,配置将被延时;如果在配置过程中变低,表示在配置过程中出现了错误;当配置结束后,这个引脚表示POST_CRC错误;

SCPn

Input

SCP0-SCP7是挂起控制引脚

CMPMOSI,

CMPMISO,

CMPCLK

N/A

保留为将来使用,可用作普通IO

M0, M1

Input

配置模式,M0=0表示并行配置模式,M0=1表示串行配置模式;M1=0表示主模式,M1=1表示从模式

CCLK

Input/

Output

配置时钟,主模式下是输出时钟,从模式下是输入时钟

USERCCLK

Input

主模式下可选的的用户输入配置时钟

GCLK

Input

全局时钟引脚,它们可当做普通IO使用

VREF_#

N/A

参考门限时钟引脚,当不用时可作为普通IO使用

MulTI-Function Memory Controller Pins

M#DQn

Input/

Output

#Bank的存储控制器数据线

M#LDQS

Input/

Output

#Bank的存储控制器数据使能引脚

M#LDQSN

Input/

Output

#Bank的存储控制器数据使能引脚N

M#UDQS

Input/

Output

#Bank的存储控制器高位数据使能

M#UDQSN

Input/

Output

#Bank的存储控制器高位数据使能N

M#An

Output

#Bank的存储控制器地址线A[0:14]

M#BAn

Output

#Bank的存储控制器块地址线BA[0:2]

M#LDM

Output

#Bank的存储控制器低数据屏蔽

M#UDM

Output

#Bank的存储控制器高数据屏蔽

M#CLK

Output

#Bank的存储控制器时钟

M#CLKN

Output

#Bank的存储控制器时钟N

M#CASN

Output

#Bank的存储控制器列地址使能

M#RASN

Output

#Bank的存储控制器行地址使能

M#ODT

Output

#Bank的存储控制器终端电阻控制

M#WE

Output

#Bank的存储控制器写使能

M#CKE

Output

#Bank的存储控制器时钟使能

M#RESET

Output

#Bank的存储控制器复位

Dedicated Pins

DONE_2

Input/

Output

带可选上拉电阻的双向信号,作为输出,它代表配置过程的完成;作为输入,拉低可用来延迟启动

PROGRAM_B_2

Input

异步复位配置逻辑

SUSPEND

Input

高电平使芯片进入挂起模式

TCK

Input

JTAG边界扫描时钟

TDI

Input

JTAG边界扫描数据输入

TDO

Output

JTAG边界扫描数据输出

TMS

Input

JTAG边界扫描模式

Reserved Pins

NC

N/A

未连接引脚

CMPCS_B_2

Input

保留引脚,不连接或接VCCO_2

Other Pins

GND

N/A

地

VBATT

N/A

只存在于LX75, LX75T, LX100, LX100T, LX150和LX150T芯片,解码关键存储器备用电源;若不使用关键存储器,则可将之连接VCCAUX、GND或者直接不连接

VCCAUX

N/A

辅助电路的供电电源

VCCINT

N/A

内部核逻辑资源

VCCO_#

N/A

#Bank的输出驱动器供电电源

VFS

Input

只存在于LX75, LX75T, LX100, LX100T, LX150,和LX150T芯片;解码器key EFUSE编程过程使用的供电电源,若不使用关键熔丝,则将该引脚连接到VCCAUX、GND或者直接不连接

RFUSE

Input

只存在于LX75, LX75T, LX100, LX100T, LX150和LX150T;用于编程的解码器key EFUSE电阻,如果不编程或者不使用key EFUSE,则将该引脚连接到VCCAUX、GND或者直接不连接

3. Spartan-6系列GTP Transceiver引脚

引脚名

方向

描述

GTP Transceiver Pins

MGTAVCC

N/A

收发器混合电路供电电源

MGTAVTTTX,

MGTAVTTRX

N/A

TX、RX电路供电电源

MGTAVTTRCAL

N/A

电阻校准电路供电电源

MGTAVCCPLL0

MGTAVCCPLL1

N/A

PLL供电电源

MGTREFCLK0/1P

Input

正极参考时钟

MGTREFCLK0/1N

Input

负极参考时钟

MGTRREF

Input

内部校准电路的精密参考电阻

MGTRXP[0:1]

Input

收发器接收端正极

MGTRXN[0:1]

Input

收发器接收端负极

MGTTXP[0:1]

Output

收发器发送端正极

MGTTXN[0:1]

Output

收发器发送端负极

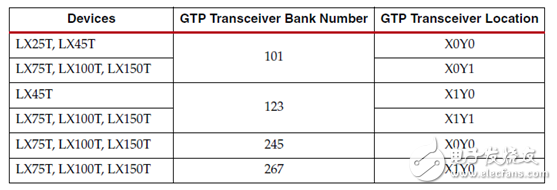

如表6所示,对LX25T,LX45T而言,只有一个GTP Transceiver通道,它的位置是X0Y0,所再Bank号为101;其他信号GTP Transceiver的解释类似。

表6:GTP Transceiver所在Bank编号

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)