由于串口在电报通信、工控和数据采集等领域有着广泛的应用,绝大多数嵌入式处理器都内置了通用异步收发器(UART)。UART数据传输主要通过中断或DMA的方式实现。

中断方式是在接收到数据或需要发送数据时产生中断,在中断服务程序中读写UART的缓冲区(FIFO)实现数据传输。由于串口通信速率一般比较低(典型值不超过115 200 bps),大多数嵌入式系统都采用中断方式来传输串口数据。然而,中断服务程序需要占用CPU的时间,而串口速度的提升也必将导致CPU更频繁地响应UART中断,这势必会造成嵌入式系统的性能下降。

DMA数据传输无需CPU的参与,是一种更加高效的数据传输方式。现有的DMA数据传输方案都是基于DMA块传输方式(即BLOCk DMA)。这种方式下每次传输完一个数据块后产生一个DMA中断,在高速串口通信中,频繁的DMA中断仍然会影响系统的性能。本文基于散列DMA(seatter DMA)的传输方式提出了一套完整的工业级高速串口驱动设计方案,实现了波特率高达12 Mbps的UART数据传输。

2 DMA数据传输的特点DMA(Direct Memory ACCess,直接存储器访问),是指数据在内存与I/O设备间的直接传输,数据 *** 作由DMA控制器(DMAC)完成而不需要CPU的参与,大大提高了CPU的利用率。因此,DMA是高速数据传输的理想方式。利用DMA进行数据传输时应注意以下几点:

①DMA传输需要占用系统总线,在此期间CPU不能使用总线。如果外设在进行数据传输时不能有任何的间断,就必须保证传输期间DMAC对系统总线的独占,这可能会影响其他需要使用总线进行数据传输的设备。所以,系统总线在DMA传输期间是否可被抢占,要依据嵌入式系统的特定环境来决定。

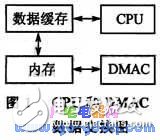

②DMA传输存在缓存一致性(cache coherency)问题。如图1所示,DMAC和CPU是两个平行的单元,CPU总是通过数据缓存来访问内存中的数据,而DMAC则直接访问内存。如果内存中的数据被DMAC更新,而数据缓存中的数据尚未被更新,CPU获得的某些地址的值可能并不是内存中的真实值。为了避免这个问题,可在DMAC更新完内存数据后或CPU读取被更新过的数据前刷新数据缓存,或是使用不被数据缓存映射的非缓存(non-cacheable)内存区域。

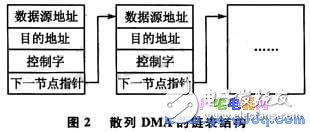

DMA数据传输可分为块传输和散列传输两种方式。在DMA传输数据的过程中,要求源物理地址和目标物理地址必须是连续的。但是在某些计算机体系中(如IA架构),连续的存储器地址在物理上不一定是连续的,所以DMA传输要分成多次完成。传输完一块物理上连续的数据后引发一次中断,然后进行下一块物理上连续的数据传输,这就是DMA块传输方式(Block DMA)。散列传输是在块传输方式上发展起来的,它与一个传输链表相关,如图2所示。该链表可以是单向结构或环形结构。控制字中包含数据位宽、数据块大小、当前块传输结束是否引发中断等控制信息。DMA块传输可看作是只含有一个节点,且下一节点指针总是指向当前节点的散列传输。采用散列DMA方式能更灵活、高效地传输数据。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)