介绍了四相序列扩频调制与解调方法,并对四相序列扩频与QPSK在高斯白噪声信道条件下进行了仿真。仿真结果表明,该方案与传统的多进制正交扩频系统相比,大幅提高了数据的传输速率和抗干扰能力,可以较好地适用于高速数据通信。

直接序列扩频方式是直接用伪噪声寻列对载波进行调制,适应信道环境比较恶劣,具有较强的抗干扰能力,因而得到了广泛的重视和应用,如测距、抗人为和自然干扰、抗衰落、低功率谱密度、抗侦听、码分多址等。与传统的直扩系统相比,多进制正交扩频系统在相同的信息速率和系统带宽条件下具有更高的扩频增益,能有效地解决传输带宽和处理增益之间的矛盾。文献中提出了一种N进制正交扩频与M进制差分相位调制相结合的复合调制方案(NOrth—MDPSK),并对其进行了性能分析。文献中还提到了双多进制正交扩频与M进制差分相位调制相结合的复合调制方案(DNOrth—MDPSK),其数据速率得到了进一步提高,但由于采用的是非相干包络和差分检测以及需要进行单双码的判别,因此性能有所下降。对此,本文提出采用四相序列扩频与BPSK相结合的复合调制方案,并对其在加高斯白噪声信道条件下进行了仿真,其结果证明了本方案的优越性。

1四相序列原理由于信道带宽的限制和抗干扰能力的要求,采用四相序列扩频技术,四相序列扩频可实现较高的扩频处理增益,而同时保持较低的信号带宽。四相序列扩频技术是选出若干组准正交扩频码,每31个扩频码携带8 bit信息进行传输。每组扩频码传送了8 bit,假如传输码率为4 Mbit.s-1,扩频后的信道符号速率是4Mbit.s-1×31 bit/8 bit=15.5 Mbit.s-1,按2倍符号速率计算传输带宽为31 MHz,实际使用中四相扩频序列经过基带成形滤波后,传输带宽可降低至28 MHz以内。

四相序列的定义:Z4={0,1,2,3}上的A族四相序列由非全零的递归方程来定义,其特征多项式是A4上的不可约本源元,其中r是特征多项式的阶数,其多项式可表示为

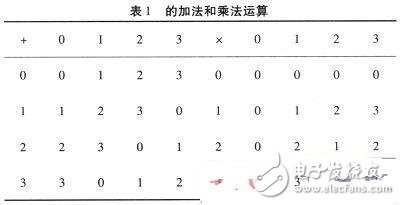

式中的加法和乘法运算是在Z4上进行的,Z4上的计算如表1所示。由于基于整数的乘法运算下只有元素1和3存在逆元,所以系数p0的选择受到限制,另外取得循环序列的关键是移位寄存器的初始状态。

以选用3阶为例,对特征多项式f(x)=x3+2x2+x+3对应置9种不同的初始值,可获得9个长度是7的四相循环序列,如表2所示。

每个初始序列经过5级移位和反馈模4的计算又可得到31个准正交序列,一共可产生279个序列,满足8 bit的256个扩频序列要求。

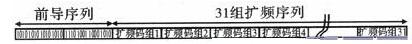

2四相序扩频技术实现为精确估计扩频序列同步头,本文对发送数据进行前导码插入。数据帧结构如图1所示,每帧数据包括32 bit的前导码和31个扩频码组,每个扩频码组是31个码元的四相序列。通过插入前导码进行相位校正,从而可以准确同步序列。

图1 调制数据帧结构示意图

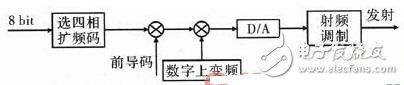

四相序扩频调制结构如图2所示。除了前导序列外,其他31组8 bit数据用来选择相应的四相序扩频码,经与前导码混合后,再经数字上变频、DA输出模拟信号,最后射频调制发射。数据码率为4:Mbit.s-1,每31个扩频码组插入32 bit同步码,每个扩频帧间隔调制的数据比特数为280,有效传输数据比特数248,从而大幅提高了数据的传输速率。由图2可知,中频信号112 MHz,经上变频到2 400 MHz输出。

图2 四相序扩频调制发送流程图

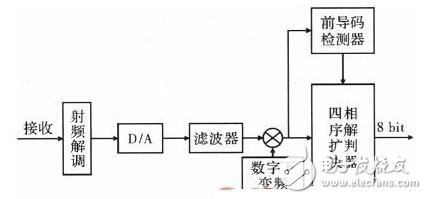

四相序扩频系统的解调单元结构如图3所示。接收信号首先经过射频解调得到复频域中频信号,经D/A量化、数字滤波和数字下变频后,一路送入前导码检测器,同时也送入四相序解扩相关器,前导码检测器找到扩频同步信号,相序解扩相关器在收到同步信号后,将接收数据和扩频序列进行相关性计算,找到对应的8 bit数据输出,其中四相序解扩模块的详细结构如图3所示。

图3 接收通道信息处理流程图

3仿真验证及结论

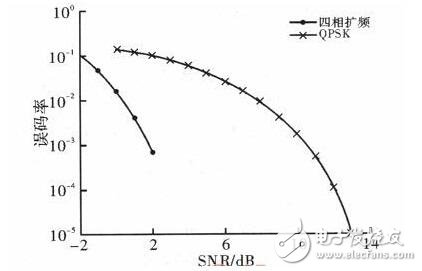

图4 四相扩频和QPSK在高斯信息下的性能仿真

对传输码率4 Mbit.s-1分别采用四相序列扩频和QPSK在高斯信道中进行了仿真。四相序扩频是每8 bit信息数据(4个QPSK符号)映射成31个码元的四相序列扩频序列(31个QPSK符号),四相序列扩频的理论增益是10log(31/4)=8.9 dB.从图4中可分析出四相序列扩频在SNR=2 dB和QPSK在SNR=11 dB时的性能相当,误码等级为7e-4.四相序列扩频在SNR》2 dB时,性能提升明显,每次以8×105个数据进行仿真,没有出现误码;相同情况下,QPSK在SNR达到13 dB时仍有误码出现。经仿真验证,四相扩频在带宽有限的情况下,四相扩频数据以8 bit进行分组,四相扩频的信道编码的性能提升比QPSK更明显,能较好地提升信号增益,减少误码率,为扩频高速通信提供良好的技术支持。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)