首先简要介绍了射频数字化短波发射机的基本原理以及AD9957芯片的主要功能,然后提出了一种利用AD9957芯片QDUC模式实现射频数字化短波发射机内部数字上变频模块和数/模转换模块的方案,对该模式下基带数据产生、时钟配置和串口编程的方法进行详细阐述,最后给出了AD9957在短波发射机中应用方案的仿真结果和硬件实测结果。

1.引言数字化短波发射机的设计思路是尽可能让数/模转换器(Digital to Analog Converter,DAC)靠近天线,尽可能用数字信号处理代替传统模拟信号处理。随着DSP、FPGA等硬件水平的提高,射频数字化短波发射机已成为现实。本文将介绍一种能完成正交上变频和数/模转换的专用芯片——AD9957,并对AD9957在射频数字化短波发射机中的应用进行分析研究。

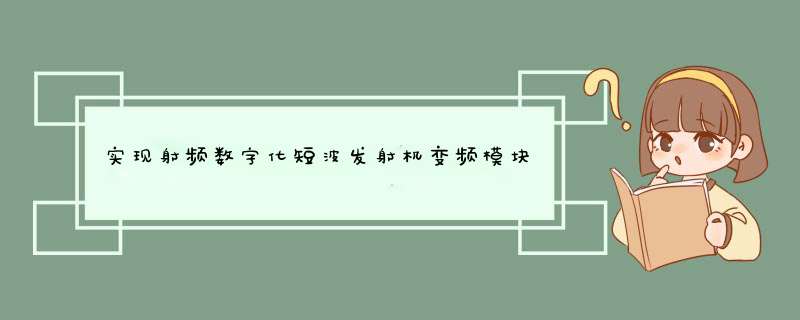

2.射频数字化短波发射机原理早期短波发射机都是模拟系统,音频输入信号经过SSB调制、多次混频、滤波和放大,音频信号才能搬移到射频频段。在射频数字化短波发射机中,大部分模拟电路被数字电路代替,基带信号直接由数字上变频模块转发至短波发射频段;DAC完成数字信号向模拟信号的转变;模拟信号经过功率放大器和匹配网络,最后由天线发射[1],如图1所示。

AD9957芯片是ADI公司生产的通用数字正交上变频器,它集成了一个高速、直接数字频率合成器(Direct Digital Synthesizer ,DDS)、一个高性能、高速的14 位DAC、时钟乘法器电路、数字滤波器和其他DSP功能[2]。AD9957有三种工作模式:正交数字上变频(Quadrature Digital Up Converter,QDUC)模式、DAC内插模式和单音模式。利用AD9957的QDUC模式,可实现射频数字化短波发射机内数字上变频和数/模转换部分。

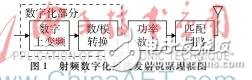

在QDUC模式中,输入正交的两路信号:I(t)和Q(t),数据分配器和格式器对I和Q进行解交错处理,以便每个样本沿着内部数据通路以并行方式传输。半带滤波器和级联梳状积分(Cascad Comb Intergrator,CCI)滤波器对基带信号进行内插滤波,分别使输入信号的采样率提高4倍和2~63倍。提高基带信号采样率的作用是能够与DDS 内核产生的正交(正弦和余弦)本振信号相乘并相加,从而产生正交上变频数据流。反CCI滤波器和反SINC滤波器分别对CCI滤波器和DAC产生的通带幅度衰减进行补偿。QDUC模式的功能框图[3]如图2所示。

/4.1I/Q数据产生

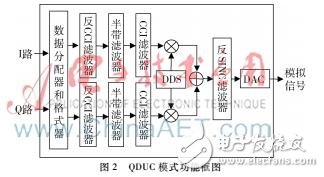

I/Q数据分别为基带数据的同相分量和正交分量,采用18位二进制补码或偏移二进制表示每个采样点的大小。基带数据的容量由数据时长和采样速率共同决定。例如,发送1 s的基带数据,采样速率为5 MHz,则需要1×5×18=90 Mbit数据容量。如果基带数据为矩形脉冲序列,在输入芯片数据端口前必须经过脉冲整形。QDUC模式下数据读取时序图如图3所示,TxENABLE是选通用户数据的信号,当信号为真时允许将数据锁存到器件中。PDCLK为并行数据时钟,该信号频率等于基带数据的采样速率。通常情况下,采用PDCLK上升沿锁存数据至数据端口。在QDUC模式下,AD9957的并行端口上交替出现I和Q数据字,每个PDCLK有效沿捕捉一个18 位I或Q字。因此,PDCLK时钟速率为:

其中,fSYSCLK是DAC的采样速率;R是CCI滤波器的插值因子。半带滤波器插值因子为定值4,CCI滤波器插值因子为R,则I或Q数据各自的速率为fSYSCLK/4R, 所以PDCLK时钟速率为fSYSCLK/2R。

4.2时钟配置

通过芯片上REF_CLK/REF_CLK输入引脚,有两种方式为AD9957提供参考时钟输入,分别是直接驱动和晶振驱动。

直接驱动允许直接输入频率在60 MHz~1 GHz之间的信号作为芯片的系统时钟。也可以输入低频信号,由芯片内部的锁相环(PLL)倍频为400 MHz~1 GHz。晶体驱动是由晶振产生参考时钟,然后倍频至相应的系统时钟频段。

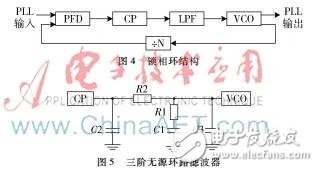

AD9957采用了一种数模混合锁相环,即电荷泵锁相环CPPLL(Charge Pump PhaseLock Loop),其基本结构如图4所示,主要由鉴频鉴相器PFD(PhaseFrequence Detector)、电荷泵CP(Charge Pump)、低通滤波器LPF(LowPass Filter)、分频器(Divider)和压控振荡器VCO(Voltage Control Oscillator)组成[4]。

LPF采用三阶环路滤波器[5],如图5所示。

图5三阶无源环路滤波器

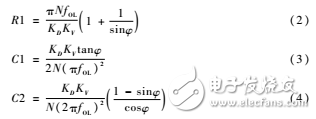

其中R2为1 kΩ,C3为1.1 pF,其余参数根据设计需要在芯片外围焊接,计算公式如下:

其中,KD为电荷泵电流值; KV为VCO增益; N为反馈分配系数;φ为相位余量; fOL为开环带宽。

在硬件测试中,取KD=287 μA,KV=500 MHz/V,N=20,fOL=1.2 MHz,φ=45°。计算得出,R1为1 211 Ω,C1为300 pF,C2为46 pF。

4.3串口编程

串行通信周期可分为两个阶段。第一个是指令阶段,将要访问的寄存器地址字节写入 AD9957,并定义第二阶段进行写入或者读取。第二阶段为写入周期或者读取周期,分别指从串行端口控制器向串行端口缓冲器传输数据和从有效寄存器读取数据。写入周期结束后,编程数据驻留在串行端口缓冲器中,处于无效状态。I/O_UPDATE 将串行端口缓冲器中的数据传输到有效寄存器。对于读取周期,不需要I/O_UPDATE,数据在时钟下降沿输出。

此外,AD9957支持 MSB 优先或 LSB 优先传输格式。串行接口端口可以配置为单脚输入/输出(SDIO)或者双脚分别输入和输出(SDIP和SDO);I/O复位(I/O_RESET)信号和低电平有效片选(CS)信号控制串口通信是否进行,提高了设计系统灵活性。

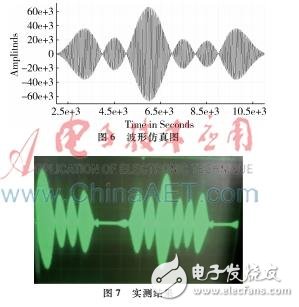

5结论采用码率为2 kb/s的自定义序列(1011010)作为基带数据,采用Systemview软件搭建QDUC模式功能电路,并进行仿真验证。仿真过程中,脉冲整形采用的升余弦滤波器滚降系数为0.5,200倍内插滤波,输出载频25 MHz,仿真结果如图6所示。

硬件测试结果如图7所示,实际测试结果和仿真结果基本一致。

综上所述,AD9957应用于短波发射机,实现射频数字化,具备实际可行性。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)