单端初级电感转换器 (SEPIC) 能够通过一个大于或者小于调节输出电压的输入电压工作。除能够起到一个降压及升压转换器的作用以外,SEPIC 还具有最少的有源组件、一个简易控制器和钳位开关波形,从而提供低噪声运行。看是否使用两个磁绕组,是我们识别 SEPIC 的一般方法。这些绕组可绕于共用铁芯上,其与耦合双绕组电感的情况一样,或者它们也可以是两个非耦合电感的单独绕组。设计人员通常不确定哪一种方法最佳,以及两种方法之间是否存在实际差异。本文对每种方法进行研究,并讨论每种方法对实际 SEPIC 设计产生的影响。

图 1 显示了耦合电感的基本 SEPIC。当FET (Q1) 开启时,输入电压施加于初级绕组。由于绕组比为 1:1,因此次级绕组也被施加了一个与输入电压相等的电压;但是,由于绕组的极性,整流器 (D1) 的阳极被拉负,并被反向偏置。整流器偏颇关闭,要求输出电容在这种“导通”时间期间支持负载,从而强迫 AC电容 (CAC) 充电至输入电压。Q1 开启时,两个绕组的电流为 Q1 到接地,而次级电流流经 AC 电容。“导通”时间期间总 FET 电流为输入电流和输出次级电流的和。

FET 关闭时,绕组的电压反向极性,以维持电流。整流器导电向输出端提供电流时,次级绕组电压现在被钳位至输出电压。通过变压器作用,它对初级绕组的输出电压进行钳位。FET 的漏极电压被钳位至输入电压加输出电压。FET“关闭”时间期间,两个绕组的电流流经 D1 至输出端,而初级电流则流经 AC 电容。

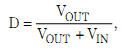

耦合电感由两个非耦合电感代替时,电路运行情况类似。要让电路正确运行,必须在每个磁芯之间维持伏-微秒平衡。也就是说,对于两个非耦合电感而言,在FET“导通”和“关闭”时间期间,每个电感电压和时间的积必须大小相等,而极性相反。通过代数方法表明,非耦合电感的 AC 电容电压也被充电至输入电压。在 FET“关闭”时间期间,输出端电感被钳位至输出电压,其与耦合电感的次级绕组一样。在 FET“导通”时间期间,AC 电容在电感施加一个与输入电压相等但极性相反的电势。每间隔时间,对电感定义电压进行钳位,这样伏-微秒平衡便决定了占空比 (D) 的大小。其在连续导通模式 (CCM) 运行时,可简单表示为:

FET 导通时,施加于输入端电感的电压等于输入电压。FET关闭时,伏-微秒平衡通过钳位其 VOUT 来维持。记住,FET 导通时,输入电压施加于两个电感;FET 关闭时,输出电压施加于两个电感。两个非耦合电感 SEPIC 的电压和电流波形,与耦合电感版本的情况非常类似,以至于很难分辨它们。

如果 SEPIC 类型之间确实存在少许的电路运行差异的话,那么我们应该使用哪一种呢?我们通常选择使用耦合电感,是因其更少的组件数目、更佳的集成度以及相对于使用两个单电感而言更低的电感要求。然而,高功率现货耦合电感有限的选择范围,成为摆在广大电源设计人员面前的一个难题。如果他们选择设计其自己的电感,则必须规定所有相关电参数,并且必须面对更长的交货时间问题。耦合电感 SEPIC 可受益于漏电感,其可降低 AC 电流损耗。耦合电感必须具有 1:1 的匝数比,以实施伏-微秒平衡。选择使用两个单独的非耦合电感,一般可以更广泛地选择许多现货组件。由于并不要求每个电感的电流和电感完全相等,因此可以选择使用不同的组件尺寸,从而带来更大的灵活性。

方程式 1 到 3 表明了耦合电感和非耦合电感的电感计算过程。

方程式计算得到最大输入电压和最小负载时 CCM 运行所需的最小电感。50% 占空比运行(VIN 等于 VOUT 时出现)和统一效率条件下,比较这些方程式可知,方程式 1 中耦合电感的计算值是非耦合电感计算值的两倍。由于转换器肯定会有损耗,而大多数输入电压源均有很大不同,因此这种简化了的电感泛化一般为错误的;但它通常足以应付除极端情况以外的所有情况。它一般意味着,转换器会比预期稍快一点进入非连续导通模式 (DCM) 运行,其在大多数情况下仍然可以接受。如前所述,使用非耦合电感时,正如我们通常假设的那样,无需输出端电感的值与输入端电感一样;但是为了简单起见肯定会这样做。利用 VOUT/VIN 调节输入端电感,便可确定输出端电感值。使用更小值输出端电感的好处是,它一般尺寸更小而且成本更低。

实例设计:

“表 1”所示规范为设计比较的基础。第一个设计使用一个耦合电感,而第二个则使用两个非耦合电感。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)