虽然可以对各种器件进行开路和短路测试,但这在半导体验证测试中最为常见。本文将详细描述在CMOS芯片上测试开路和短路的过程。

在深入研究开路和短路测试的技术细节之前,我们必须首先了解其与半导体验证的相关性。半导体验证通常分为结构和功能两部分。结构测试可确保芯片正确构建。功能测试确定芯片是否符合设计规范并在最终环境中按预期执行。打开和短路测试检查半导体芯片的保护二极管电路中的故障。因此,它是一种结构测试。

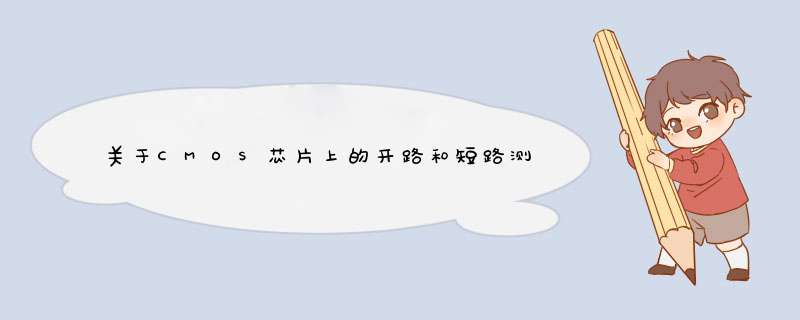

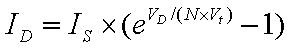

下图表示典型的CMOS芯片。可以看出,每个引脚都具有保护二极管和CMOS晶体管的网络。

图1: CMOS芯片的内部电路

每个输入引脚上的CMOS晶体管通过允许电流从V DD(芯片的电源电压)流入DUT电路以及从DUT电路流向V SS(地)来起到开关的作用。如果在输入或输出引脚上感应出过压,可能会损坏CMOS晶体管。为了保护这些器件,每个信号引脚都放置了两个二极管(参见图1)。第一个位于信号引脚和V DD之间,第二个位于信号引脚和V SS之间。如果在任何引脚上施加大于V DD的正过压,则V DD二极管变为正向偏置,允许电流在信号引脚和V DD之间流动。类似地,如果在任何引脚上施加大于V SS的负过压,则V SS二极管变为正向偏置,允许电流在V SS和信号引脚之间流动。这样,保护二极管可防止在过压条件下损坏CMOS晶体管和DUT电路。V DD和V SS保护二极管必须在开路和短路条件下进行测试,以确保其正常工作。如果保护二极管缺失或功能不正常,可能会出现开路情况。如果存在直接连接,则可能出现短暂情况:

引脚和V DD之间

引脚和V SS之间

引脚和另一个信号引脚之间

这些短路故障模式中的每一种都妨碍了设备的正确 *** 作。打开并短接所有上述故障模式的测试检查。

注:CMOS集成电路基于FET技术,因此通常使用V DD / V SS术语来确定正电源电压/负电源电压(接地)。这些端子也可以记录为V CC / Gnd。

1.第1节:硬件设置测试设置

开路和短路的测试设置分为两个例程:测试V DD保护二极管和测试V SS保护二极管。

测试V DD保护二极管

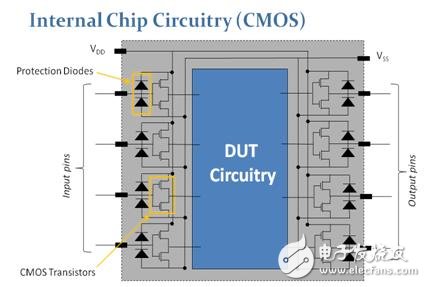

为了检测信号引脚的V DD保护二极管的开路或短路,将V SS,V DD和所有其他信号引脚连接到SMU地,并将最小电流(即100μA)强制插入信号引脚。如果V DD保护二极管正常工作,它将变为正向偏置,电流将在信号引脚和V DD之间流动(见图2)。

图2:测试VDD二极管(开关未显示)

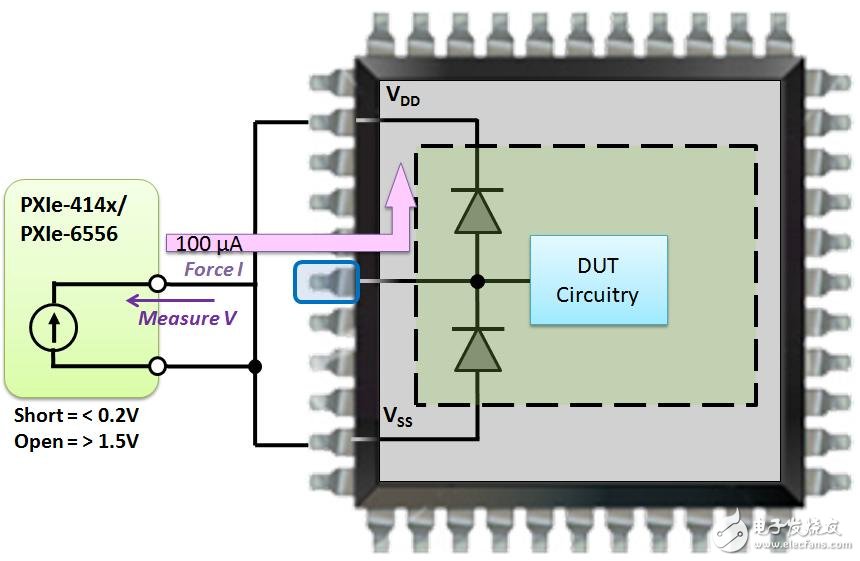

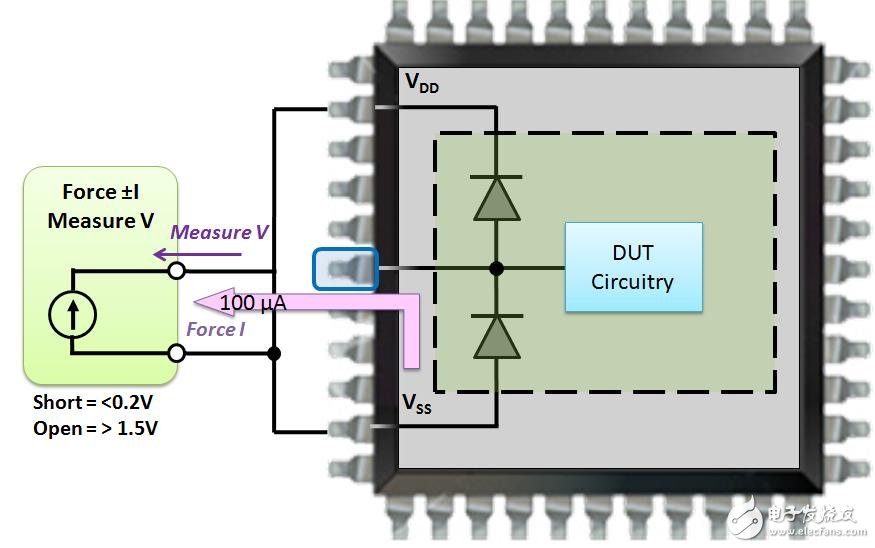

通过测量正向偏置V DD二极管两端的压降,我们可以确定它是否正常工作。如果信号引脚和地之间测量的电压接近0 V(或接地),则信号引脚与地之间通过V SS,V DD和/或另一个信号引脚之间存在一个或多个短路。如果在信号引脚之间测量的电压或上升到高于可接受的正向偏置电压的电位,则信号引脚和地之间存在开路。如果测得的电压是可接受的正向偏压,则V DD保护二极管正常工作。表1显示了V DD的示例 保护二极管测试结果和由此产生的通过/失败规范。

注意: 没有电流(除少量漏电流外)流过V SS保护二极管,因为它会反向偏置。

注意: 可接受的正向偏压通常取决于制造半导体二极管的材料。然而,制造技术也可用于降低正向偏置电压降。硅二极管的正向偏压通常被认为是0.65 V.精确的电压降取决于流过二极管pn结的电流,结的温度和几个物理常数。正向偏置电压降,施加电流和相关变量之间的关系如下图3所示,通常称为二极管方程:

图3:二极管方程

二极管方程中的变量如下所述。ID =二极管电流(A)IS =饱和电流(A)VD =二极管两端的电压降(V)N =理想系数,介于1和2 Vt之间=热电压(V),室温下约25.85 mV两者之间的电压信号引脚和地将接近0 V,测试结果将为Fail:Shorted。如果其他信号引脚未全部接地,电流仍会流过正向偏置的V DD保护二极管(如图2所示),测试结果为Pass。

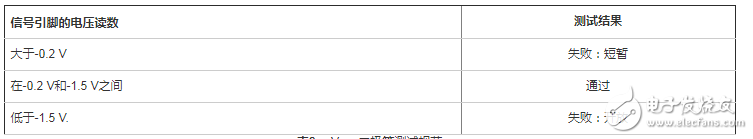

测试V SS保护二极管

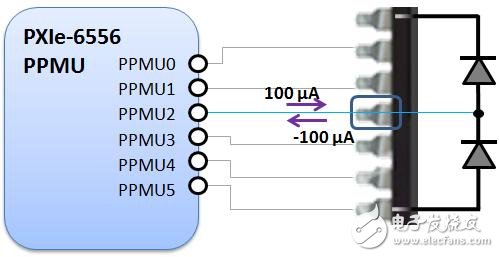

测试V SS二极管的过程与测试V DD二极管的过程相同。所有引脚(包括V SS和V DD)都连接到SMU地。然而,这次,相同值的负电流(即-100μA)被强制进入信号引脚。如果V SS保护二极管正常工作,它将变为正向偏置,电流将在V SS和信号引脚之间流动(见图4)。

图4:测试VSS二极管(开关未显示)

注意:没有电流(除了少量漏电流)流过V DD保护二极管,因为它会反向偏置。

通过测量正向偏置V DD二极管两端的压降,我们可以确定它是否正常工作。表2列出了V SS保护二极管的测试参数。

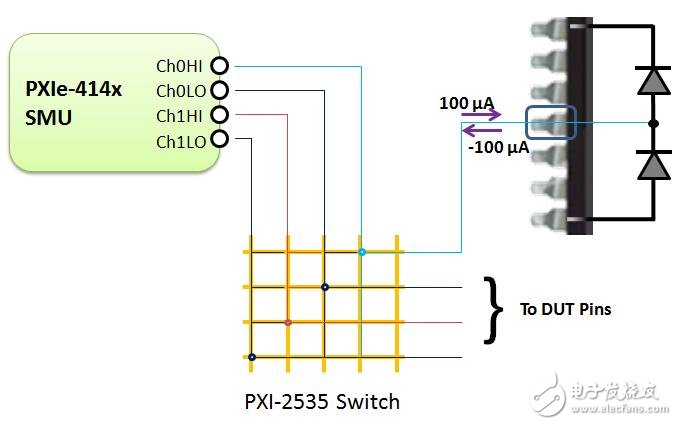

自动化测试设置

有两种常见的硬件配置可用于执行开路/短路测试。首先,外部开关系统前端和可编程源测量单元可用于自动化V DD和V SS保护二极管测试。开关系统可以扫描预先配置的状态,创建到半导体器件的V DD,V SS和信号引脚所需的电流和接地路径。源测量单元可以强制所需的电流并测量从每个信号引脚到地的结果电压(见图5)。其次,除了交换系统外,还可以使用PXIe-6556,也可以使用卡的PPMU功能在数字引脚上使用。选项一将在下面详细讨论。

图5a:使用SMU和MUX进行Opens / Shorts自动测试设置

图5b:使用HSDIO打开/短接自动测试设置

以下步骤概述了使用上述SMU和开关组合进行开路和短路测试的过程:

第1步:将所有引脚接地

为了通过FET开关将SMU连接到DUT,使用矩阵拓扑结构,其中SMU的引脚连接到矩阵中的行,而引脚来自芯片连接到列。

通过关闭矩阵上的所有连接来完成DUT上所有引脚的接地,该连接将PXI-4130 SMU的地线连接到DUT上的引脚。从PXI-4130 SMU低引脚到V DD和V SS的连接直接通过电缆而不是通过开关完成。这是因为V DD和V SS引脚始终连接到SMU低引脚。虽然所有信号引脚最初都连接到SMU Low,但它们依次连接到SMU测量通道,因此通过矩阵开关连接到SMU。

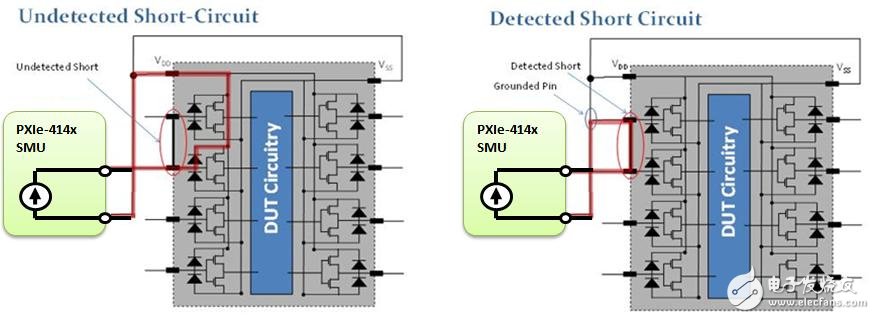

重要的是不仅要将V SS和V DD连接到地。在测试保护二极管之前,所有其他信号引脚应接地。将所有其他信号引脚接地可确保检测到任何信号引脚到信号引脚短路。有关进一步说明,请参见图6。当在两个信号引脚之间检测到短路时,被测引脚和SMU低电压之间的电压应该超出表1和表2中列出的可接受范围(理想情况下为0V),测试应该失败。如果其他信号引脚未全部接地,则电流仍会流过正向偏置的V DD保护二极管,测试结果为Pass。见下面的图6。

[+]放大图片

图6:接地引脚对于检测短路至关重要

步骤2:在3 V的SMU上设置电压钳

为了在开路条件下产生的极限电压,在SMU上设置上限电压钳位。如果未设置钳位且电路开路,则SMU将测量非常高的电压值。这可能会损坏芯片电路。在PXI-4130上,电压钳位电平在软件中设置为3 V. 3 V是可接受的值,因为它高于检测开路(1.5V)的测试限值,并且在大多数CMOS的规格范围内芯片。

步骤3:从SMU强制±100uA并测量产生的电压

SMU每次向一个信号引脚的二极管施加±100μA的电流,并测量产生的电压。每个引脚通过矩阵开关依次连接到SMU。对于该测试,预期电压约为±0.65V(正向偏置二极管两端的电压降)。测量由强制电流产生的电压并与测试规格表进行比较,以确定最终的测试结果。

回到顶部2.第2节:软件设置

该开放和短路系统的软件是使用NI LabVIEW和NI Switch ExecuTIve开发的。LabVIEW用作主应用程序开发环境(ADE),而Switch ExecuTIve用于配置高密度矩阵上的路由。

以下软件版本用于实施Opens and Shorts Semiconductor测试:

LabVIEW 8.5图形编程环境

Switch ExecuTIve 2.1.1交换机管理软件

可以从本文档末尾的链接下载本文档中描述的LabVIEW代码。

注意: LabVIEW图形化编程语言中的功能块称为“虚拟仪器”或“VI”。因此,在描述本节中的过程时将使用首字母缩略词‘VI’。

如前所述,开路和短路测试可分为两个例程:a)测试V DD保护二极管,b)测试V SS保护二极管。两个例程都可以使用相同的硬件连接来执行,并且编程例程的唯一区别可以是简单地改变SMU的强制电流的方向。由于这些相似之处,本文档仅概述了演示如何测试V SS保护二极管的示例。该测试程序可以复制并稍作改动,以测试V DD保护二极管。有关必要变更的详细信息,请参见文件末尾。

测试V SS保护二极管的步骤如下:

初始化,配置和启用SMU输出

初始化开关硬件并将所有DUT引脚连接到地

使用5544交叉点FET矩阵迭代信号引脚

断开被测信号引脚与地之间的连接

将SMU连接到被测信号引脚

测量被测信号引脚和地之间的电压

对测量的电压进行分析以确定测试结果

断开SMU与被测信号引脚的连接

将被测信号引脚重新接地

禁用SMU的输出并关闭SMU会话句柄

从开关硬件断开所有信号引脚并关闭NISE会话句柄

初始化SMU,配置和启用SMU的输出

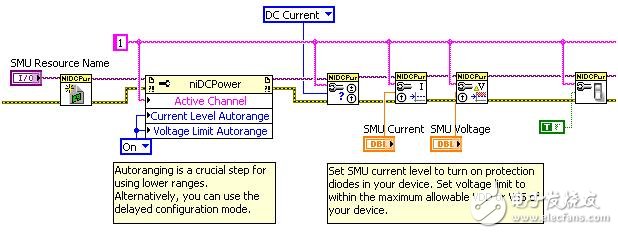

使用LabVIEW中的NI-DCPower API初始化,配置和启用PXIe-4141 SMU的输出。有关框图代码的图片,请参见图7。

图7:在LabVIEW中初始化,配置和启用SMU输出

SMU的资源名称被送入IniTIalize VI以初始化SMU并提供SMU会话句柄。然后将SMU会话句柄传递给所有后续的NI-DCPower VI。接下来,SMU的通道1配置为DC电流,这是它将进行测试的原因。NI-DCPower配置VI可以按任何顺序连接,只要在启用SMU输出之前设置所有参数即可。需要馈送的参数包括电流水平,电流水平范围,电压限制和电压限制范围。

Initialize VI之后的步骤是niDCPower属性节点。该步骤指示SMU根据电流水平和电压限制输入自动确定和设置电流水平和电压限制范围。属性节点后面的VI确认SMU将用于DC电流模式。接下来,将电流水平设置为-100μA(测试V SS保护二极管,配置通道1,使电流流入SMU,V SS保护二极管正向偏置)和电压限制,或者电压钳位设置为3 V(相当于±3 V)。

最后,输入到配置输出启用VI的布尔值true启用SMU的输出,将配置参数提交给设备并开始通过SMU的通道1的-100μA电流。

初始化开关硬件并将所有DUT引脚连接到地

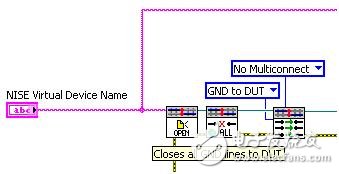

初始化开关硬件并将其设置为V DD,V SS和所有DUT的信号引脚接地的状态。使用LabVIEW控制开关有多种方法,但是将系统切换硬件编程的最佳方法是使用NI Switch Executive API。有关框图代码的图片,请参见图8。

图8:初始化开关硬件并将所有DUT引脚连接到地

NI Switch Executive(NISE)虚拟设备名称被输入到Open Session VI,以打开系统中所有交换机的会话句柄。NI Switch Executive将这些会话句柄存储在一个NISE会话句柄中,该句柄传递给所有后续的NISE VI。“断开所有”VI断开NI Switch Executive会话管理的每个交换机设备上的所有连接,从而将交换机系统配置设置为未连接交换机路由的已知状态。最后,GND到DUT路由组中的所有路由都被连接,这导致开关硬件被设置为V DD,V SS和所有DUT的信号引脚接地的状态。

要了解有关NI Switch Executive Virtual Device的更多信息以及如何创建一个,请查看本文末尾链接的7分钟NI Switch Executive演示。

迭代信号引脚,一次测试一个

使用LabVIEW‘For Loop’迭代DUT信号引脚。在“For Loop”中,使用NI Switch Executive VI将被测DUT信号引脚与地断开,并将待测DUT信号引脚连接到SMU的通道1。使用NI-DCPower VI测量每个DUT信号引脚与地之间的电压。在继续下一次For循环迭代之前,将待测DUT信号引脚从SMU的通道1断开,然后将其重新连接到地(参见图9)。

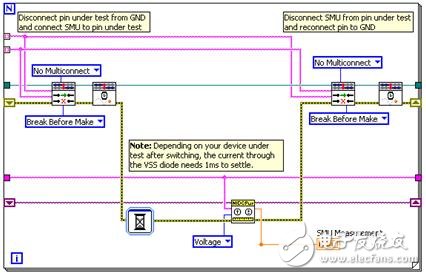

图9:断开GND,连接SMU,测量,断开SMU和重新连接GND

在上图中,我们:

断开被测信号引脚与地之间的连接

将SMU连接到被测信号引脚

测量被测信号引脚和地之间的电压

根据电压测量确定测试结果

断开SMU与待测DUT信号引脚的连接

将待测DUT信号引脚重新接地

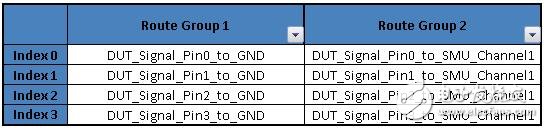

使用NI Switch Executive中创建的路由组完成断开和重新连接DUT信号引脚的过程。路由组用于将交换矩阵置于所需状态。要了解有关路由组的更多信息以及如何创建一个视图的更多信息,请参阅本文档末尾的7分钟NI Switch Executive演示。第一个路由组包含将DUT信号引脚连接到地的路由,第二个路由组包含将DUT信号引脚连接到SMU的通道1的路由(参见图10)。

图10:设置路由组以简化索引正确的DUT信号引脚

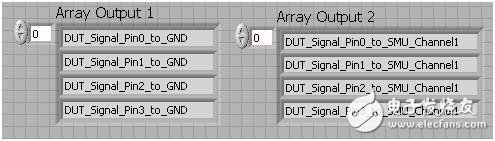

接下来,LabVIEW中的NI Switch Executive配置API提供对所有NI Switch Executive功能的完全编程访问,用于从所有路由组中提取单个路径名称。结果将是两个字符串数组,包括路由组1和路由组2的路由(参见图11)。

图11:使用NI Switch Executive Configuration API的阵列输出

将这些数组传递给For循环将自动索引数组。例如,在循环的第一次迭代中,要在循环内连接和断开的索引路由是DUT_Signal_Pin0_to_GND和DUT_Signal_Pin0_to_SMU_Channel1。在循环的第二次迭代中,索引路由是DUT_Signal_Pin1_to_GND和DUT_Signal_Pin1_to_SMU_Channel1。这将继续,直到数组索引每个元素。您不限于此命名方案。您可以在“Switch Exec for OS”VI的“路由组1”和“路由组2”控制字段中输入您的特定阵列名称。

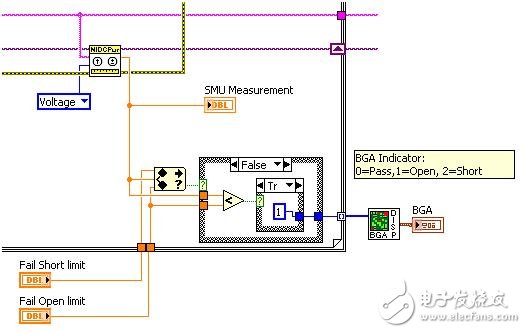

根据DUT的通过/失败规范,确定电压测量是否表明DUT信号引脚上的V SS保护二极管已经通过,失效打开或因短路而失效(见图12)。

图12:根据电压测量确定测试结果

在进行电压测量并确定测试结果后,断开SMU的通道1与被测DUT信号引脚的连接,并将被测引脚重新接地。

禁用SMU的输出并关闭SMU会话句柄

使用NI-DCPower VI禁用SMU的输出并关闭SMU会话句柄。有关框图代码的图片,请参见图13。

图13:禁用SMU输出并关闭SMU会话句柄

输入到配置输出启用VI的布尔值false禁用SMU的输出,停止通过通道1的-100μA电流。关闭VI关闭SMU会话句柄并重新分配先前保留的SMU资源。

注意: 如果在调用关闭VI时仍然启用了电源输出,则通道1将保持其当前状态并继续吸收电流。

从开关硬件断开所有信号引脚并关闭NISE会话句柄

使用NI Switch Executive VI断开V DD,V SS和其余信号引脚与交换硬件的连接并关闭NISE会话句柄。有关框图代码的图片,请参见图14。

图14:断开所有信号引脚并关闭NISE会话句柄

Disconnect All VI再次断开NI Switch Executive会话管理的每个交换机设备上的所有连接,从而将交换机系统配置设置为未连接交换机路由的已知状态。Close Session VI关闭系统中所有交换机的会话句柄。虽然不是必需的,但包含错误处理程序通常很有帮助。如果发生错误,VI将返回错误描述,并可选择显示包含错误信息的对话框。

修改代码以测试V DD保护二极管

要修改V SS保护二极管测试,必须首先禁用SMU,然后在重新启用SMU之前,应更改配置以在通道1上强制100μA而不是-100μA。For循环可以执行完全相同的连接和断开,进行测量并确定测试结果。

结合V SS和V DD保护二极管测试

确定每个DUT信号引脚的最终结果可以通过组合V SS和V DD保护二极管测试的结果来完成。只有当两个保护二极管都通过各自的测试时,才能确定通过的最终结果。有多种方法可以显示测试结果,包括但不限于a)将布尔值传递到LED阵列,以及b)在数组中格式化和显示字符串簇。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)