引言

超声波电机(USM)具有能够直接输出低转速大力矩,瞬态响应快(可达ms量级)、定位精度高(可达nm量级),无电磁干扰等诸多优点。USM的运行需要有两路具有一定幅值,相位上正交(或可调),频率在20 kHz以上的高频交流电源。驱动信号源的幅值、频率及相位直接影响USM的性能。为便于USM的性能测试及研究,需要提供一种在幅值、频率、相位上均可调的测试电源。以往的超声波驱动器多采用分立器件构成如文献,其电路结构复杂。文献虽然改用FPGA或CPLD生成,但所生成的信号频率变化是不连续的。文献是用单片机和专用的DDS芯片,存在抗干扰性差,可靠性低的弊端。

本文介绍了基于DLL数字频率直接合成技术(DDS)用ALTERA公司的FPGA器件和VHDL语言编程,按相位累加的方法产生两相四路频率相位可调的高频PWM信号,经过驱动电路、光耦隔离电路作为外部功率控制电路H桥的四个闸门驱动信号,H桥主回路接入的是对市电经调压、隔离、整流及滤波后的直流电。由闸门驱动信号对该直流电进行通断控制,形成可调幅值、频率、相位差的两相高频PWM波的交流信号,再经外加电感平滑,将PWM波信号变成类正弦波信号,实现对USM的性能测试。

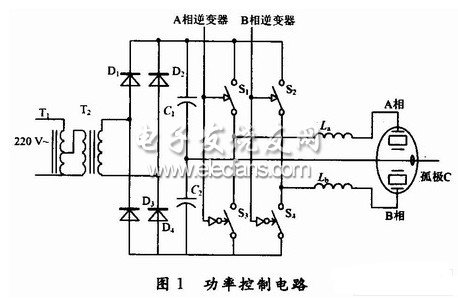

1 功率控制电路

如图1所示,加于USM的A、B两相交流信号是由FPGA产生的四路脉冲信号控制MOS管开关对整流滤波后直流电进行通断控制,在图1所示H桥逆变器的作用下,将直流电逆变为与逆变器开关频率相同的矩形波交流电,经串联电感平滑,就得到了USM所需的两相高频类正弦波信号。该信号可由主回路的调压器调节幅值,A、B两相的相位差取决于H桥两侧闸门驱动信号的相位差,即闸门S1与S2(或S3与S4)驱动信号的相位差。同侧桥臂不能同时导通,以避免大电流通过MOS开关管而损坏开关管,理论上同侧的两个控制信号应该相位互补,实现推挽输出,考虑到开关器件的延时特性,该信号开启闸门时要有一定的延时,即死区时间。鉴于以上分析及USM性能测试的需求,闸门控制信号应具有频率、相位、死区时间均可调的占空比大于50%的PWM高频波。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)