系统设计工程师常被要求降低总体功耗,以减少对我们环境的影响,同时降低投资和运营成本。他们还需要提高电路密度,以便实现外形尺寸更小的电子系统,并且能在更严苛的环境下工作。遗憾的是,若将高功耗解决方案整合到这些系统中,会带来极大的散热问题,而使得其他目标也无法实现。

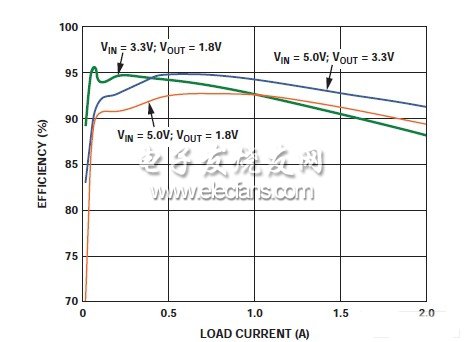

图1 ADP2114开关稳压器的典型效率

DC/DC转换器的效率虽然比LDO高很多,但DC/DC转换器在直接为高速模数转换器供电时,往往由于噪声太大而会导致性能大幅下降。这种噪声至少有两种来源:通过电源纹波直接进入转换器的噪声,以及由于磁耦合效应引起的噪声。电源纹波在ADC的输出频谱中以不同的音调(或者杂散)出现,或者导致底噪全面提高。ADC对这些不同音调的易感性可以进行表征,通常在转换器数据手册中以电源抑制比(PSRR)表示。但是PSRR无法表示对转换器底噪的宽带效应。开关电源中产生的大电流通常会产生很强的磁场,该磁场会与电路板上的其他磁性元件产生耦合,包括匹配网络中的电感,以及用于耦合模拟和时钟信号的变压器等。进行电路板布线时必须小心仔细,以防这些磁场与关键信号耦合。

省电(效率优势)

虽然半导体公司一直在推出更高效率的ADC、DAC和放大器,但是与用DC/DC稳压器替代LDO所获得的总系统功效相比,这些改进实在是微乎其微。这里以一个采用3.3V电源提供100mA电流或者330mW功率的线性电路为例,采用将5 V降压调节至3.3 V的典型LDO时,总功耗将为500mW,而仅有330mW提供有用功。原始电源必须比实际所需的电源大51%,这样既浪费能源又增加了成本。通过比较,不妨考虑效率为90%的DC/DC稳压器。5V电源的总电流要求将为74mA(这是一个更低得多的要求),可同时降低了功耗和成本。

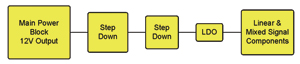

在无线基站等系统中,电源通常由单个高电流电源提供。该电源通常通过大量不同的降压级向下降压调节,然后再到达线性和混合信号元器件。尽管每个降压级的效率都很高,但是它们也会浪费相当多的功率。图2显示了一个电源从12V电源轨进行降压调节的典型系统,其使用了三个或更多降压级为ADC和其他模拟器件提供电源。最后一级一般是LDO,通常,这一级的效率在降压级中最低。当按下图所示级联两次之后,即使是效率为90%的高效率DC/DC稳压器也仅能达到81%的效率,而最后的稳压级必须是LDO时,效率则会更低。

图2 典型的系统级电源

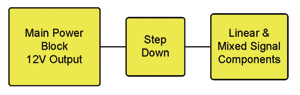

随着DC/DC电源技术的进步以及更高开关频率的发展,DC/DC电源实现了在不造成性能损失的情况下,以大幅提高的效率直接为ADC供电。图3显示了省去LDO的典型降压电路。

图3 简化的系统级电源

此外,许多系统为每个ADC采用单独的LDO。单独的LDO用于提供不同ADC之间的噪声隔离,并降低每个LDO的功耗。这种单独提供的方式分散了LDO产生的热量,并且可使用小封装形式的LDO。由于开关转换器具有更高的效率,因此一个开关可为多个ADC和其他线性元件供电,而不会产生过多功耗和热量,而采用单个大LDO则会发生这种情况。在开关电源的输出端采用滤波铁氧体磁珠可为采用相同电源轨的元件提供隔离。采用开关电源减少了系统对稳压器的需求,由于省去了多余的LDO及其相关电路,因而可明显实现省电以及降低电路板成本。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)