英特尔瞄准人工智能已是显而易见的事情了,毕竟错过移动市场加上PC市场日渐不给力,找寻有活力、有潜力的新兴市场实属情理之中的事情。但作为半导体IDM巨头,英特尔也没有落下制程工艺推进的事业,虽然目前看起来台积电、三星的制程更为领先,已经可以量产10nm,但别忘了去年夏天曾爆出过的半导体制造巨头间的制程并不对等这一情况。

英特尔制程更先进?

说到制程就不得不提纳米(nm),那么什么是纳米呢?这是一个单位,也就是1米的十亿分之一。用一个指甲来作比喻的话,那就是说试着把一片指甲的侧面切成10万条线,每条线就约等同于1纳米,由此可略为想像得到1纳米是何等的微小了。

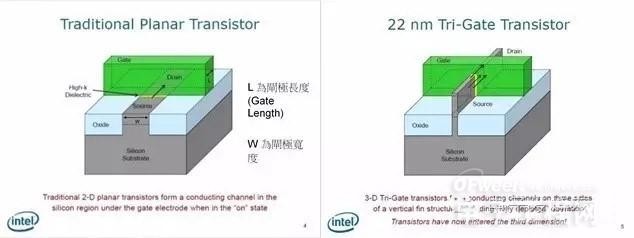

就拿14nm制程来说,这里所指14nm的,是指在芯片中,线最小可以做到14纳米的尺寸,下图为传统电晶体的长相,以此作为例子。缩小电晶体的最主要目的就是为了要减少耗电量,然而要缩小哪个部分才能达到这个目的?左下图中的L就是我们期望缩小的部分。藉由缩小闸极长度,电流可以用更短的路径从Drain端到Source端。

英特尔14nm工艺与台积电、三星同代工艺比较

但实际上线宽定义半导体工艺先进程度并不准确,更有意义的是栅极距(gate pitch)、鳍片间距(Fin Pitc)等,英特尔早前就对比过他们与台积电、三星的16、14nm工艺,如上图所示,英特尔的14nm工艺在这些关键指标上要比三星、台积电好得多,这两家的工艺其实有些名不副实,落后Intel差不多半代水平。

三星、台积电在半导体工艺命名上赢过了英特尔,这实际上是商业宣传的胜利,技术上超越英特尔还有点名不正言不顺,对这个问题业界早前就有过争议了,不过这事有没有什么强制性约束,如何命名更多地是厂商自己的事,大家也只能听之任之了。

在这样的背景下,英特尔昨天发了一条很有意思的文章:让我们清理半导体工艺命名的混乱吧。文章的作者是Mark Bohr,英特尔高级院士,也是处理器架构与集成部门的主管,可以说是资深的业界专家了,他在这篇文章中就指出了业界在半导体工艺命名上的混乱之态。

当然,他的重点不是批评现状,而是给出了一个更合理的衡量半导体工艺水平的公式,如下图所示:

英特尔给出的衡量半导体工艺先进程度的公式

这个公式挺复杂的,Bohr院士指出衡量半导体工艺真正需要的是晶体管密度,这个公式分为两部分,一部分计算2bit NAND(4个晶体管)的密度,另一部分更为复杂,计算的是SFF(scan flip flop)的晶体管密度,0.6和0.4两个数字是这两部分的加权系数。

Bohr院士希望半导体厂商在介绍工艺节点时也应该公布逻辑芯片的晶体管密度,而且还有一个重要的参数:SRAM cell单元面积,考虑到每家厂商的工艺都不同,在NAND+SFF密度之外最好还要独立公布SRAM面积。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)