当涉及到计算运营成本和电信基础设施项目的碳足迹时,功耗成为一个越来越重要的变量。例如,在美国平均每个满负荷3G基站的费用大约为1600美元/年,或在欧洲大约为3200美元/年。这表明,一个典型的欧洲运营商运行2万个基站会消耗58MW功率,折算为每年6200万美元左右。除了这些费用,每个基站的功耗估计为每年每个基站有11吨二氧化碳的排放量。对于这些运营商,功耗就是成本。 FPGA已经成为基站结构的最重要的组成部分之一,所以人们关注FPGA的焦点是使功耗降至最低。

例如,为了尽量减少功耗,LatTIceECP3 FPGA系列采用可变的沟道长度,优化的低功耗晶体管,以及改进的布线默认和算法。结果在典型设计中,与同类拥有SERDES功能的FPGA的竞争产品相比较,ECP3的静态功耗减少了80%,总功耗减少了50%多。

系统设计人员在使用FPGA时通常要考虑FPGA的四部分的功耗:

预编程的静态(静态)器件的功耗

预编程的静态器件的功耗是指FPGA在编程之前的功耗。即当FPGA已上电,但处于未编程的状态时,这就是静态器件的功耗。重要的是在此期间该器件不会消耗大

浪涌编程电流:(浪涌电流/对器件编程直到编程结束时所需要的功耗)

在过去,浪涌电流编程一直是FPGA厂商面对的问题。浪涌编程电流实际上已超过一个典型应用的功耗,以及实际的额定电源/稳压器功率。这当然是不可取的,莱迪思对设计产品投入了相当大的精力,使编程电流(浪涌)处于任何典型应用的功耗之下。莱迪思在数据手册和功耗计算器工具中说明并跟踪了浪涌的情况。

后编程的静态功耗: ‘零MHz ’频率时器件的功耗

编程后静态功耗是FPGA功耗的重要组成部分。这是由于在FPGA中有大量的晶体管(通常为8至10倍于用同等的ASIC逻辑来实现的数量,配置和多路复用器不包括在内),所有这些器件都有少量的泄漏电流。无论晶体管是否被使用,这些晶体管的漏电流(用于切换的复用器,RAM单元等)通常是“永远存在的”,并吸收功率。通常情况下,编程后静态功耗等于或大于静态器件功耗。有一些最新的创新解决功耗网格的方法,去除这些特殊晶体管的功耗,这将减少这部分的静态功耗。

动态功耗:非零频率所增加的功耗。 (即P = kcV2f)

动态功耗遵循kcV2f规则,通常受设计人员的控制。根据正在实施的不同类型的设计(始终开启,时刻处理,设计的数据路径的类型对比唤醒、处理和返回睡眠的设计类型等),无论是动态功耗,还是编程后的静态功耗都是功耗分析中的最重要组成部分。

功耗是与温度密切相关的。随着FPGA的自身发热,由于晶体管的漏电流的增加,功耗随之增加。在极端的情况下,器件非常热以至晶体管不能关闭,这种情况被称为热失控。功耗分析被视为任何FPGA设计过程中的至关重要的一部分。使用功耗分析,设计人员会确信设计将工作于设计环境之中。使用各种技术方法用以控制温度,如风扇、散热片、修改设计,I/O标准等。

建立 “模拟环境”的功耗模型

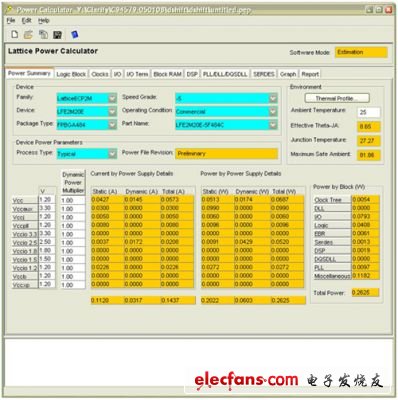

除了FPGA架构的改进之外,在低功耗设计过程中,基于软件的工具是很有价值的。例如,莱迪思的功耗计算器(图1),包含了模拟环境的功耗模型,工具中拥有图形化的功耗显示和多种有用的报告。热电阻可选模型模拟了真实的各种热的情况,包括散热片,气流及印刷电路板的复杂性,而图形化的功耗曲线反映了工作温度。印刷电路板组装后,基于软件的功耗计算器可用于前,后FPGA设计过程,以分析所预期的功耗。

图1功耗计算器可用于设计周期中的任何阶段。切换率的早期估计以后可以用模拟结果来取代。精确的功耗计算器计算所有结构单元的电流和功耗,并提供热模型,以模拟真实的系统条件

总结

成功的低功耗设计是取决于结构还是工艺?答案不是传统的观点认为是正确的东西。先进的工艺并不能够保证低功耗:在结构和电路设计阶段提出的折衷方案对最终的结果是至关重要的。如果FPGA针对性能而优化,必将导致更高的整体功耗。对于把高性能的电路放在哪些绝对需要的地方,设计人员必须做出权衡,同时针对低功耗,优化芯片的其他区域。传统的FPGA厂商仅期望下一个工艺节点以获得可估量的更小的功耗。然而,65纳米的LatTIceECP3表明它有可能比40/45nm的竞争器件具有更低的功耗。在这种模式转变的核心是安排了巧妙的电路和晶体管设计。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)