当论及在不同处理器或内存之间提高芯片之间的传输流量时,光子学是一个热门的话题。截至目前为止,微波导、光调变器、输出耦合光闸与光探测器均已成功进行整合了,但要设计理想的微米级光源仍十分具有挑战性。

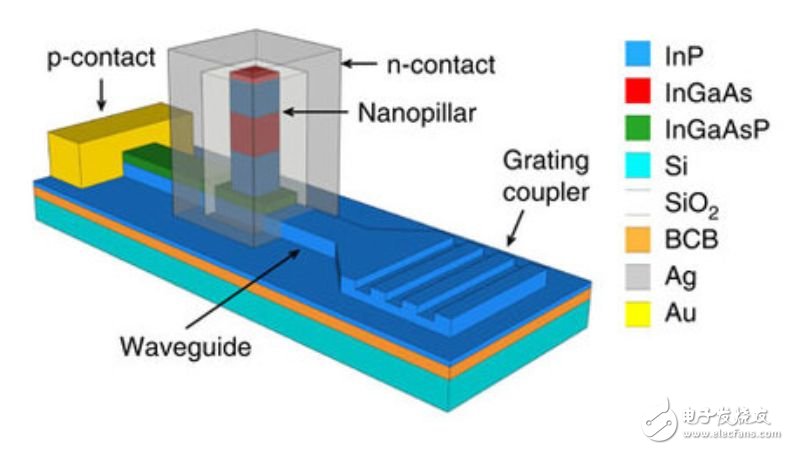

荷兰爱因霍芬科技大学(Eindhoven University of Technology)的研究人员在最近一期的《自然通讯》(Nature CommunicaTIons)期刊中发表有关「芯片上波导耦合纳米柱金属腔发光二极管」(Waveguide-coupled nanopillar metal-cavity light-emitTIng diodes on silicon)的最新研究。研究人员展示一种接合至硅基板的纳米级LED层堆栈,并可耦合至磷化铟(InP)薄膜波导形成光闸耦合器。

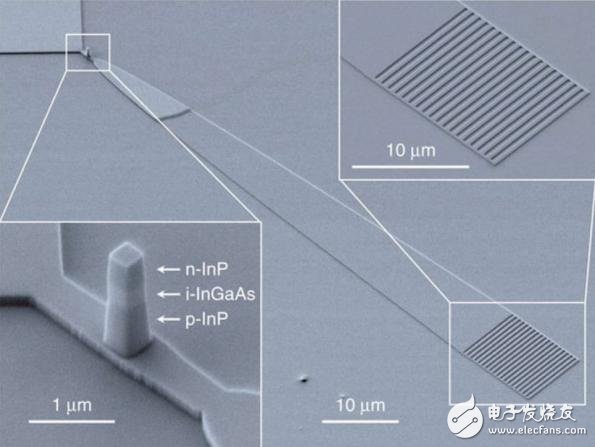

新式纳米级LED (nano-LED)的扫描式电子显微镜图(SEM)显示在金属化之前的制造组件结构。纳米柱LED位于连接至光闸耦合器的波导顶部

这种nano-LED采用次微米级的纳米柱形状,其效率可较前一代组件更高1,000倍,在室温下的输出功率仅几奈瓦(nW),相形之下,先前的研究结果约为皮瓦(pW)级输出功率。根据该研究论文显示,这种组件能够展现相当高的外部量子效率(室温分别为10^−4~10^−2,以及9.5K)。

而在低温时,研究人员发布的功率级为50nW,相当于在1Gb/s速率下每位传输超过400个光子,这一数字「远远高于理想接收器的散粒噪声(shot-noise)极限灵敏度。」该组件作业于电信波长(1.55μm),能以频率高达5GHz的脉冲波形产生器进行调变。

硅基板上的纳米柱状LED示意图。从顶层到底层的堆栈分别是:n-InGaAs(100 nm)/n-InP(350 nm)/InGaAs(350 nm)/p-InP(600 nm)/p-nGaAsP(200 nm)/InP(250 nm)/SiO 2/BCB/SiO2/Si

研究人员表示,「由于短距离互连的损耗低,以及整合接收器技术持续进展,这一功率级可望以超精巧的光源实现芯片内部的数据传输。」

研究人员还开发了一种表面钝化方法,能够进一步为nano-LED提高100倍的效率,同时透过改善奥姆接触(ohmic contact)进一步降低功耗。

编译:Susan Hong

(参考原文:nano-LED could support mulTI-Gbit/s on chip traffic,by Julien Happich)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)