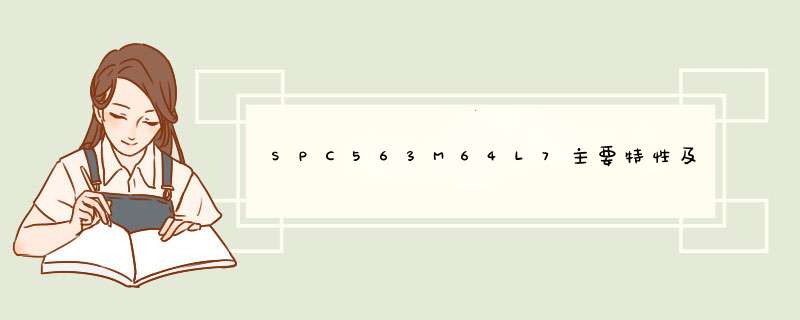

ST公司的SPC563M64L7是用于汽车动力总成的32位Power Architecture MCU,是系统级芯片(SoC),采用许多新特性的高性能90nm CMOS技术,以降低成本和提高性能,Power Architecture®技术具有支持DSP的附加指令,以及诸如增强的时间处理单元,增强排队的模数转换器,控制局域网(CAN)和增强的模块输入/输出系统.此外,器件还集成了94KB SRAM和1.5MB闪存.本文介绍了SPC563M64L7主要特性,框图,以及SPC563Mxx系列Discovery Plus开发板SPC563M-DISP主要特性和电路图,PCB顶层布局图.

These 32-bit automoTIve microcontrollers are a family of System-on-Chip (SoC) devices that contain many new features coupled with high performance 90 nm CMOS technology to provide substanTIal reducTIon of cost per feature and significant performance improvement. The advanced and cost-efficient host processor core of this automoTIve controller family is built on Power Architecture® technology. This family contains enhancements that improve the architecture’s fit in embedded applications, includes additional instruction support for Digital Signal Processing (DSP), integrates technologies—such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system—that are important for today’s lower-end powertrain applications. The device has a single level of memory hierarchy consisting of up to 94 KB on-chip SRAM and up to 1.5 MB of internal flash memory. The device also has an External Bus Interface (EBI) for ‘calibration’。

SPC563M64L7主要特性:

Single issue,32-bit Power Architecture® Book E compliant e200z335 CPU core complex

– Includes Variable Length Encoding (VLE) enhancements for code size reduction

32-channel Direct Memory Access controller (DMA)

Interrupt Controller (INTC) capable of handling 364 selectable-priority interrupt sources: 191 peripheral interrupt sources, 8 software interrupts and 165 reserved interrupts.

Frequency-Modulated Phase-Locked Loop (FMPLL)

Calibration External Bus Interface (EBI)(a)

System Integration Unit (SIU)

Up to 1.5 Mbyte on-chip Flash with Flash controller

– Fetch Accelerator for single cycle Flash access @80 MHz

Up to 94 Kbyte on-chip static RAM (including up to 32 Kbyte standby RAM)

Boot Assist Module (BAM)

32-channel second-generation enhanced Time Processor Unit (eTPU)

– 32 standard eTPU channels

– Architectural enhancements to improve code efficiency and added flexibility

16-channels enhanced Modular Input-Output System (eMIOS)

Enhanced Queued Analog-to-Digital Converter (eQADC)

Decimation filter (part of eQADC)

Silicon die temperature sensor

2 Deserial Serial Peripheral Interface (DSPI) modules (compatible with Microsecond Bus)

2 enhanced Serial Communication Interface (eSCI) modules compatible with LIN

2 Controller Area Network (FlexCAN) modules that support CAN 2.0B

Nexus Port Controller (NPC) per IEEE-ISTO 5001-2003 standard

IEEE 1149.1 (JTAG) support Nexus interface

On-chip voltage regulator controller that provides 1.2 V and 3.3 V internal supplies from a 5 V external source.

Designed for LQFP144, and LQFP176

The SPC563Mxx series microcontrollers are system-on-chip devices that are built on Power Architecture® technology and:

Are 100% user-mode compatible with the Power Architecture instruction set Contain enhancements that improve the architecture’s fit in embedded applications

Include additional instruction support for digital signal processing (DSP)

Integrate technologies such as an enhanced time processor unit, enhanced queued analog-to-digital converter, Controller Area Network, and an enhanced modular input-output system

Operating Parameters

– Fully static operation, 0 MHz

– 80 MHz (plus 2% frequency modulation - 82 MHz)

– –40 C–150 C junction temperature operating range

– Low power design

Less than 400 mW power dissipation (nominal)

Designed for dynamic power management of core and peripherals

Software controlled clock gating of peripherals

Low power stop mode, with all clocks stopped

– Fabricated in 90 nm process

– 1.2 V internal logic

High performance e200z335 core processor

Advanced microcontroller bus architecture (AMBA) crossbar switch (XBAR)

Enhanced direct memory access (eDMA) controller

Interrupt controller (INTC)

– 191 peripheral interrupt request sources, plus 165 reserved positions

– Low latency—three clocks from receipt of interrupt request from peripheral to interrupt request to processor

Frequency Modulating Phase-locked loop (FMPLL)

Calibration bus interface (EBI) (available only in the calibration package) System integration unit (SIU) centralizes control of pads, GPIO pins and external interrupts.

Error correction status module (ECSM) provides configurable error-correcting codes (ECC) reporting

Up to 1.5 MB on-chip flash memory

Up to 94 KB on-chip static RAM

Boot assist module (BAM) enables and manages the transition of MCU from reset to user code execution from internal flash memory, external memory on the calibration bus or download and execution of code via FlexCAN or eSCI.

Periodic interrupt timer (PIT)

– 32-bit wide down counter with automatic reload

– 4 channels clocked by system clock

– 1 channel clocked by crystal clock

System timer module (STM)

– 32-bit up counter with 8-bit prescaler

– Clocked from system clock

– 4 channel timer compare hardware

Software watchdog timer (SWT) 32-bit timer

– 16 standard timer channels (up to 14 channels connected to pins in LQFP144)

– 24-bit timer resolution

Second-generation enhanced time processor unit (eTPU2)

– High level assembler/compiler

– Enhancements to make ‘C’ compiler more efficient

– New ‘engine relative’ addressing mode

Enhanced queued A/D converter (eQADC)

– 2 independent on-chip RSD Cyclic ADCs

– Up to 34 input channels available to the two on-chip ADCs

– 4 pairs of differential analog input channels

2 deserial serial peripheral interface modules (DSPI)

– SPI provides full duplex communication ports with interrupt and DMA request support

– Deserial serial interface (DSI) achieves pin reduction by hardware serialization and deserialization of eTPU, eMIOS channels and GPIO

2 enhanced serial communication interface (eSCI) modules

2 FlexCAN modules

Nexus port controller (NPC) per IEEE-ISTO 5001-2003 standard IEEE 1149.1 JTAG controller (JTAGC)

图1.SPC563Mxx系列框图

SPC563Mxx系列Discovery Plus开发板SPC563M-DISP

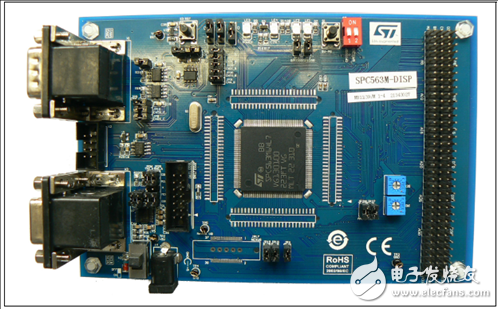

The SPC563M-DISP Discovery kit helps you to discover SPC56 M line Power Architecture® Microcontrollers. The discovery board is based on SPC563M64L7, a 32-bit Power Architecture Book E compliant e200z335 CPU core with 1.5Mbyte on-chip in an LQFP176 package. The numerous interfaces including CAN/SCI/K-LINE/DSPI/GPIO make the SPC56M-Discovery an excellent starter kit for customer quick evaluation and project development. The SPC56 M family is designed to address cost sensitive powertrain and transmission applications. The SPC56 M line key functionality is Time processing units (eTPU) a coprocessor to create events in sync with internal or external signals without flooding the CPU with interrupt to serve.

图2.Discovery Plus开发板SPC563M-DISP外形图

图3.Discovery Plus开发板SPC563M-DISP硬件概述图

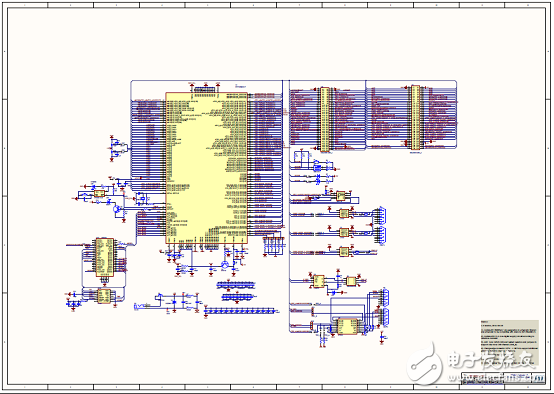

图4.Discovery Plus开发板SPC563M-DISP电路图

图5.Discovery Plus开发板SPC563M-DISP顶层PCB布局图

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)