The MAC57D5xx family is the next generaTIon platform ofdevices specifically targeted to the instrument cluster marketusing single and dual high resoluTIon displays.

Leveraging the highly successful MPC56xxS product family, NXP is introducing a mulTI-core architecture powered by ARMCortex-M (for real TIme) and Cortex-A processors (for applications and HMI), coupled with 2D Graphics Accelerators(GPU), Head Up Display (HUD) Warping Engine, Dual TFT display drive, integrated Stepper Motor Drivers and a powerfulI/O processor, that will offer leading edge performance and scalability for cost-effective applications.

Powered by ARMR CortexR -M and Cortex-A processors, coupled with 2D graphics accelerators, HUD warping engine,Dual TFT display drive, integrated Stepper Motor Controller and a powerful I/O processor, these products offer leadingperformance and scalability for cost-effective applications.

The family supports up to 2 WVGA resolution displays, including one with in-line Head up Display (HUD) warpinghardware. Graphics content is generated using a powerful Viviane GPU supporting OpenVG1.1, and the 2D Animation andComposition Engine (2D-ACE), which significantly reduces memory footprint for content creation. Embedded memories include up to 4 MB Flash, 1 MB SRAM with ECC and up to 1.3 MB of graphics SRAM without ECC. Memory expansion isavailable through DDR2 and SDR DRAM interfaces while two flexible QuadSPI modules provide SDR and DDR serialFlash expansion. In response to the growing desire for security and safety, MAC57D5/4xx family integrates NXP’s latestSHE-compliant CSE2 engine and delivers support for ISO26262 ASIL-B functional safety compliance.

MAC57D5xx主要特性:

• ARM™ Cortex-A5, 32-bit CPU

– Supports ARMv7- ISA

– 32 KB Instruction cache, 32 KB Data cache

– NEON SIMD Media Processing Engine

– FPU supporting double precision floating pointoperations

– Memory Management Unit

– GIC Interrupt Controller

– Up to 320 MHz

• ARM™ Cortex-M4, 32-bit CPU

– Supports ARMv7 - ISA

– 16 KB Instruction cache, 16 KB Data cache

– 64 KB Tightly-Coupled Memory (TCM)

– Single Precision FPU

– NVIC Interrupts Controller

– 1.25 DMIPS per MHz integer performance

– Up to 160 MHz

• I/O Processor

– ARM™ Cortex-M0+, 32-bit CPU

– Intelligent Stepper Motor Drive

• Memory subsystem

– System Memory Protection Unit

– 4 MB on-chip flash supported with the flashcontroller

– 1 MB on-chip SRAM with ECC

– 1.3 MB on-chip Graphics SRAM with FlexECC

• Supports wake-up from low power modes via theWKPU controller

• On-chip voltage regulator

– External 3.3 V input supply

– Option for direct, external supply of core voltage

– Low Voltage Detect (LVD) and High Voltage

Detect (HVD) on various supplies and regulators

• Debug functionality

– Run-time debug control of cores and visibility ofsystem resources using the Debug Access Port(DAP)

– IEEE 1149.1/ IEEE 1149.7 System JTAG Controller(SJTAG)

– Program and Data Trace support (16-bit data width)implemented by the ARM Trace Port Interface Unit(TPIU) Trace capture

• Timer

– Four 8-channel Flextimer modules (FTM)

– Two 4 channel System Timer Module (STM)

– Three Software WatchDog Timers (SWT)

– One 8 channel Periodic Interrupt Timer (PIT)

– Autonomous Real Time Counter (RTC)

• Analog

– 1 x 24 channel, 12-bit analog-to-digital converter(ADC)

– 2 analog comparators (CMP)

• Security

– Cryptographic Services Engine (CSE)

• Safety

– ISO26262 ASIL-B compliance

– Password and Device Security (PASS) supportingadvanced censorship and life-cycle management

– One Fault Collection and Control Unit (FCCU) tocollect faults and issue interrupts

• Multiple operating modes

– Includes enhanced low power operation

• Memory interfaces

– 2 x Dual QuadSPI Serial flash controllers

– Supports SDR and DDR serial flash

– Support for 3.3 V Hyperflash (Spansion)

– DRAM controller supporting SDR and DDR2

• Clock interfaces

– 8-40 MHz external crystal (FXOSC)

– 16 MHz IRC (FIRC)

– 128 kHz IRC (SIRC)

– 32 kHz external crystal (SXOSC)

– Clock Monitor Unit (CMU)

– Frequency modulated phase-locked loop (FMPLL)

– Real Time Counter (RTC)

• Graphics interfaces

– Vivante GC355 GPU supporting OpenVG 1.1

– 2 x 2D-ACE Display Controllers (with inline Head-Up-Display warping)

– Digital RGB, TCON_0 (RSDS), TCON_1 and OpenLDI/LVDS output options

– Digital Video Input (VIU4)

– RLE Decoder for memory-memory decompression

– 40x4 segment LCD driver, reconfigurable as 38x6 or 36x8

• Cluster peripherals

– Sound Generator Module (SGM)

– 6 Stepper Motor Drivers with Stepper Stall Detect

• Communication

– Ethernet 10/100 + AVB (ENET)

– MLB50

– FlexCAN x 3

– DSPI x 5

– LINFlexD x 3 (1 x Master/Slave, 2 x Master only)

– I2C x 2

• eDMA controller with multiple transfer request sources using DMAMUX

• Boot Assist Flash (BAF) supports internal flash programming

图1.MAC57D5xx高等级框图

图2.MAC57D5xx详细框图

MAC57D5xx评估板MAC57D5MB

This user guide details the setup and configuration of the NXPMAC57D5xx Mother Board (MB) Customer EvaluationBoard (hereafter referred to as the EVB) and its daughter cards(208 LQFP and 516 BGA)。

The EVB is intended to provide a low cost mechanism forcustomer evaluation of the MAC57D5xx family ofmicrocontrollers, and to facilitate hardware and softwaredevelopment. The EVB is intended for bench / laboratory useand has been designed using ambient temperature specifiedcomponents. Two daughter cards are available which connectto the EVB via high-density connectors. Please consult yourNXP representative for more details.

This product contains components that may be damaged byelectrostatic discharge. Observe precautions for handlingelectrostatic sensitive devices when using this EVB and associated microcontroller.

MAC57D5xx评估板MAC57D5MB主要特性:

• Master Power switch and regulators status LED’s.

• High Speed CAN transceiver

• LIN interface

• Ethernet PHY and RJ45 socket configurable as RMII or MII

• 20-pin JTAG

• ARM Cortex Connector

• ART ETM Connector

• User RESET switch with reset status LED.

• User LED’s

• User pushbutton switches

• Potentiometer connected to analogue input channel.

• VIU Interface

• TFT Display interface with Backlight power supply for EastRising - ER-TFT050-3

• 2 Stepper Motors Connectors

图3.评估板MAC57D5MB外形图

图4.评估板MAC57D5MB元件分布图

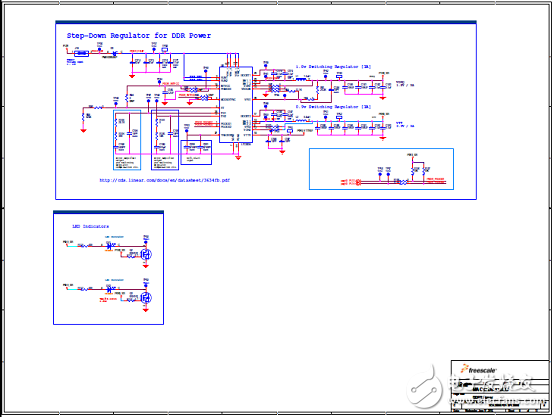

图5. 评估板MAC57D5MB电路图(1)

图6. 评估板MAC57D5MB电路图(2)

图7. 评估板MAC57D5MB电路图(3)

图8. 评估板MAC57D5MB电路图(4)

图9. 评估板MAC57D5MB电路图(5)

图10. 评估板MAC57D5MB电路图(6)

图11. 评估板MAC57D5MB电路图(7)

图12. 评估板MAC57D5MB电路图(8)

图13. 评估板MAC57D5MB电路图(9)

图14. 评估板MAC57D5MB电路图(10)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)