设计开关模式电源时,最麻烦的部件是RCD缓冲器。设计RCD缓冲器的传统方法没有主开关的关断瞬态期间的详细说明。因此,传统方式设计中的设计等式也不完全正确。本文将介绍设计和分析反激式转换器的RCD缓冲器的新方法。谐振坐标提供了一个了解主开关关断瞬态期间的简单方式,并有助于轻松设计和分析RCD缓冲器。

1. 引言

从商业上讲,反激式转换器因结构简单、尺寸紧凑、重量轻和成本低而得到广泛使用。但是它的主开关执行硬开关 *** 作,导致主开关上有较高的电压尖峰和振荡。主开关的电压应力视电压尖峰大小而增加。为减少电压尖峰以便使用更低成本的低额定电压的MOSFET,最广泛的方法是RCD缓冲器网络。即使缓冲器电压随缓冲器电阻降低而降低,但缓冲器网络上的功耗增加,导致总系统效率降低。因此,RCD缓冲器网络应优化以同时符合主开关电压应力和总系统效率两个要求。

本文将先介绍由主变压器的漏电感而产生的电压尖峰的传统分析。将介绍描述关断瞬态期间的简单方式用于进一步分析。缓冲器电流将在缓冲器坐标中分析,以便提供更详细的设计等式。

2. RCD缓冲器设计和分析

2.1 RCD缓冲器设计的一般方法

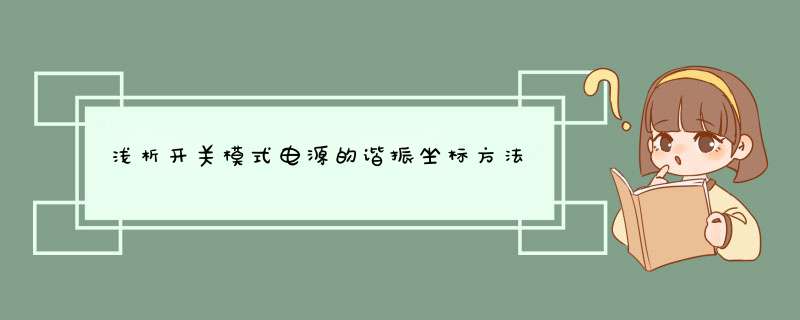

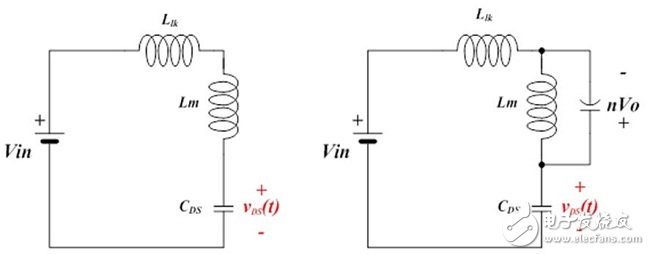

图1显示具有RCD缓冲器的传统反激式转换器。

图1:传统反激式转换器

RCD缓冲器电路用于箝位由漏电感Llk和主开关漏极至源极的电容CDS之间的谐振导致的电压尖峰。有多种假定来描述工作原理以设计RCD缓冲器,如下所示:

(1) Vsn》nVout和Vsn由于较大的Csn而几乎恒定:

(2) CDS=COSS+CTRANS,无论vDS(t)如何都恒定:

(3)当主开关Q1关闭时,无次级端漏电感,因此iDS(t)可瞬时传输至次级端二极管电流iD1(t),其中Csn是缓冲器电容,CDS是主开关漏极和源极之间的有效电容,COSS是MOSFET的输出电容,CTRANS是变压器一次电路端子之间的有效电容,vDS(t)是主开关间的电压,iDS(t)是流过主开关的电流,而Q1是主开关。

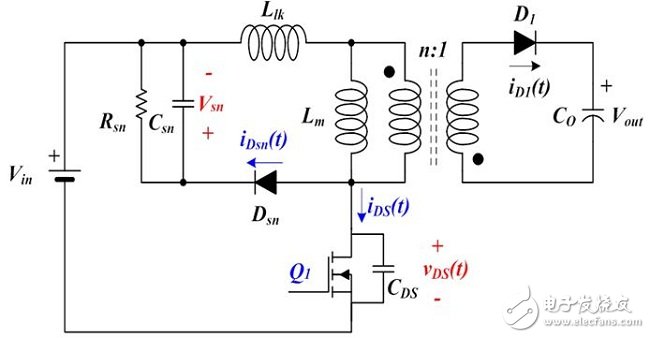

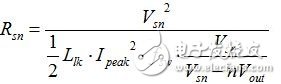

图2显示缓冲器二极管传导时的等效电路。

图2:缓冲器二极管接通期间的等效电路

当开关Q1关闭时,主电流对Q1的COSS充电(同时对变压器的CTRANS放电)。当COSS被充电至Vin+nVout时,次级端二极管接通,能量传输至次级端,并且对COSS持续充电,因为漏电感Llk仍有一些剩余能量。当Q1的vDS(t)增加至Vin+Vsn,缓冲器二极管Dsn接通,vDS(t)箝位在Vin+Vsn。当Dsn传导时,Llk上的电压为Vsn-nVout,这样Dsn(ts)的导通时间可获取如下:

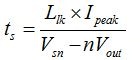

(1)

(1)

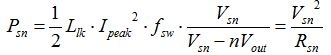

其中Ipeak是关闭开关Q1之前的峰值漏极电流。有两种方式计算缓冲器网络中的功耗(Psn);通过Dsn提供的电源和Rsn中的功耗,如下所示:

(2)

(2)

其中fsw是反激式转换器的开关频率。因此,缓冲器电阻Rsn可由下列等式获得:

(3)

(3)

这是查找缓冲器电阻Rsn的传统方式。但是,L-C谐振几步后,峰值漏极电流Ipeak被降低了一些。因此,等式(3)可能误导被过度设计的系统。

让我们使用谐振坐标得出实际峰值漏极电流,以避免在下一节过度设计RCD缓冲器。

2.2 谐振坐标中的RCD缓冲器设计和分析

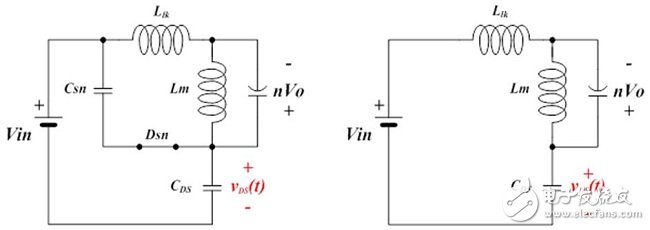

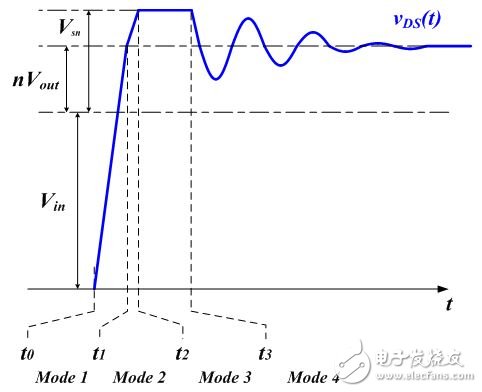

本节将使用谐振坐标设计RCD缓冲器。仅设计缓冲器时,无需分析整个反激式 *** 作模式。图3显示每个模式的等效电路,图4显示反激式转换器中的开关MOSFET的vDS(t)。

图3:关闭主开关后显示的每个模式的等效电路(按顺序依次为模式1至4)

图4:关闭开关后的vDS(t)

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)