1.概述

功率MOSFET最初是从MOS集成电路发展起来的,它通过增加源漏横向距离提高器件耐压,从而实现集成电路中高压驱动。功率MOSFET已大量应用于电力电子,消费电子、汽车电子和水声工程等领域。虽然功率MOSFET具有效率高、结构简单、便于数字化控制等优点,但是其采用的电力电子器件对过压过流的承受能力较差,容易烧毁,因此保护电路的设计非常重要,并且要求保护响应时间做到微秒级。功率MOSFET保护主要是指过流保护,对于过压的情况一般采用吸收电路来进行抑制。

在水声发射机功率MOSFET的设计和使用中,常常由于输入信号的异常和环境干扰,而导致功率放大器容易烧毁。

针对功率MOSFET易受损或烧坏的情况,在水声发射机应用中专门设计了一种以CPLD(复杂可编程逻辑器件)为核心器件的可编程保护电路。目前CPLD已经得到广泛应用。它具有体系结构/逻辑单元灵活、处理速度快、集成度高、可实现较大规模电路、编程灵活、设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定、可实时在线检验以及适用范围广等优点,因此逐步被应用于各类保护电路设计中。

鉴于CPLD的诸多优点,本设计采用单独CPLD芯片为核心,不需要单片机或DSP进行控制,来解决以MOSFET为核心的大功率发射机激励信号异常或故障所带来的严重问题,为发射机的MOSFET电路的安全稳定运行起到保护作用。CPLD保护电路在输入高电平长脉冲、连续信号和短周期脉冲等典型异常信号情况下,通过简单改变代码参数就可以防止异常的信号进入到后级损坏功率MOSFET,实现对电路的保护作用。

2.功率MOSFET基本原理

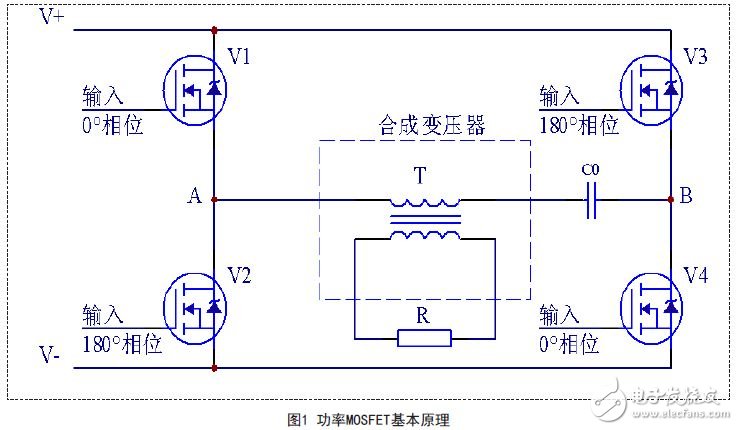

功率MOSFET电路的基本原理是:采用V1,V2,V3和V4四只可关断的功率器件组成一个H桥型丁类开关放大器(如图1所示)。图1中,对角的2只功率器件(V1和V4,V2和V3)同时导通和关断。同一侧(V1和V2,V3和V4)的器件交替导通和关断,且激励信号相差180.这样,当上边的器件关断(导通)时,下边的就导通(关断)。因此输出A,B两点的电位按照输入激励信号设定的频率(或脉宽),轮流在电源的“+”和“-”之间切换。

功率MOSFET在实际应用过程中,电路上存在高电压和大电流,并且回路上的分布电容和分布电感都很大,功率器件门极激励信号稍有故障就会在功率回路上引起过电压(或过电流)而烧毁设备或器件。所以,这种功率放大器不仅要有完备的过压过流保护功能,更重要的是要求输入至功率放大器桥路上的功率器件门极激励信号稳定可靠[4]。

3.保护电路CPLD实现

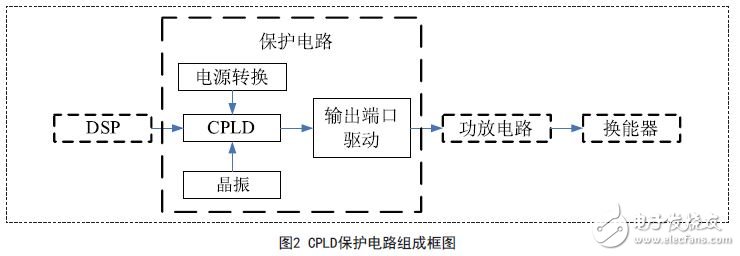

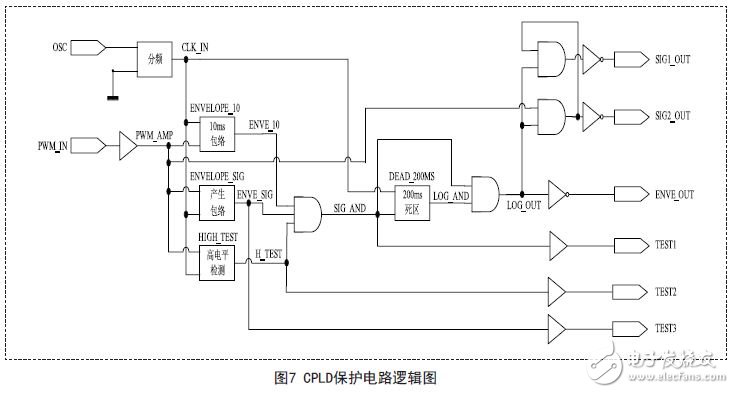

CPLD保护电路的内部主要由电源转换,晶体振荡器,CPLD,输出端口驱动等部分组成。

保护电路组成框图如图2所示。

保护电路的核心部分主要是一个CPLD,所有的功能都是通过对此器件进行逻辑编程来实现。硬件上是对来自DSP电路的模拟输出脉冲进行信号转换和保护,对应的输出为两路驱动信号和一路包络信号。两路输出信号包络相同,时间同步,信号高低电平相反。包络信号就是两路输出信号的包络,时间同步。两路输出信号经过光隔隔离并反相后为功率MOSFET提供发射激励信号源,包络信号经光隔后为功率电路提供控制信号。

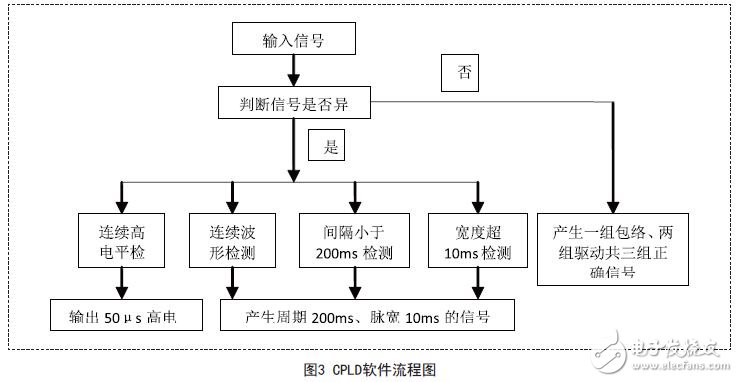

CPLD保护电路主要对输入MOSFET电路的典型异常信号,包括连续波信号、短周期脉冲信号和高电平长脉冲信号进行输入保护。所有异常输入信号通常由这三种信号组合而成。假设连续波信号是超过10ms脉冲宽度的信号;短周期脉冲信号是小于200ms脉冲周期的信号。对其他不同参数异常信号的处理,可通过简单设置软件计数器来改变。保护电路软件流程图如图3所示。

保护电路的具体保护功能与时序图如下所示:

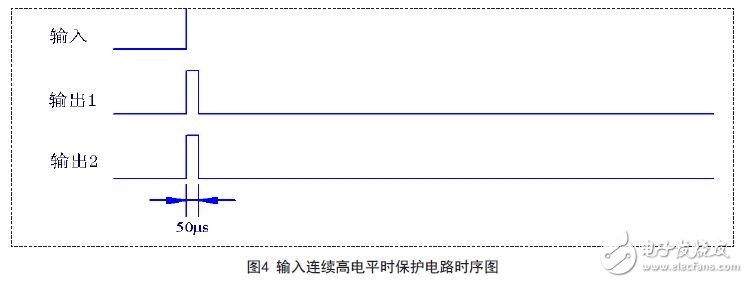

当DSP电路给保护电路输入连续高电平,保护电路会以第一个上升沿为基准,开始检测10kHz频率信号的第一个周期(即100μs),如果没有下跳沿,保护输出50μs长高电平后,关闭输出端口,保持低电平,两路驱动信号输出和输入时序如图4所示。

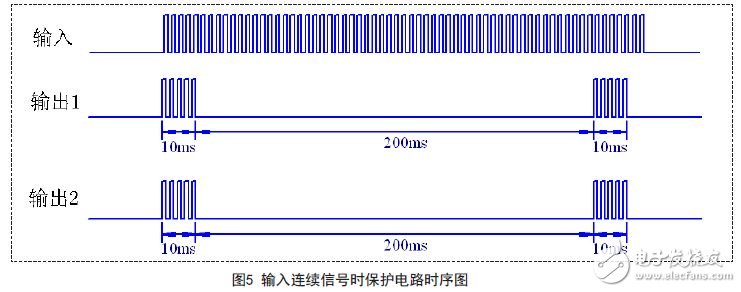

若DSP电路给保护电路输入连续波形信号,保护电路将会以第一个上升沿为基准,每隔200ms输出一个10ms的脉冲波,避免连续工作损坏功率MOSFET,两路驱动信号输出和输入信号时序如图5所示。

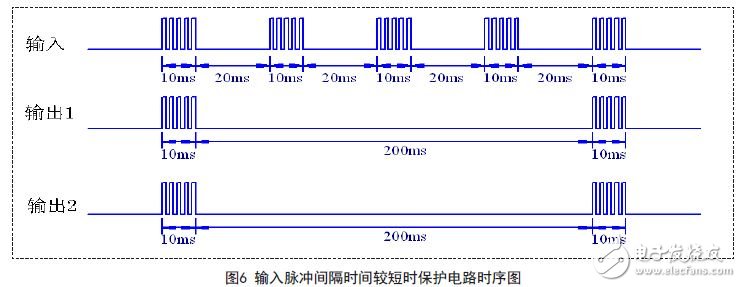

若输入信号两脉冲之间的间隔小于200ms,保护模块在第一个脉冲输入之后将会管制200ms的时间,保持在这200ms以内持续低电平后恢复正常,响应下一个脉冲信号的到来,以脉冲信号的周期为20ms为例。两路驱动信号输出和输入时序如图6所示。

CPLD保护电路实现的逻辑图见图7所示。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)