带隙是导带的最低点和价带的最高点的能量之差。也称能隙。带隙越大,电子由价带被激发到导带越难,本征载流子浓度就越低,电导率也就越低

带隙主要作为带隙基准的简称,带隙基准是所有基准电压中最受欢迎的一种,由于其具有与电源电压、工艺、温度变化几乎无关的突出优点,所以被广泛地应用于高精度的比较器、A/D或D/A转换器、LDO稳压器以及其他许多模拟集成电路中。带隙的主要作用是在集成电路中提供稳定的参考电压或参考电流,这就要求基准对电源电压的变化和温度的变化不敏感。

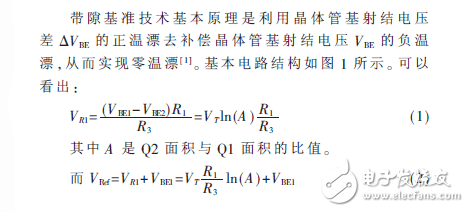

带隙基准技术基本原理基准电压源已成为大规模、超大规模集成电路和几乎所有数字模拟系统中不可缺少的基本电路模块。基准电压源可广泛应用于高精度比较器、A/D和D/A转换器、随机动态存储器、闪存以及系统集成芯片中。带隙基准电压源受电源电压变化的影响很小,它具备了高稳定度、低温漂、低噪声的主要优点。

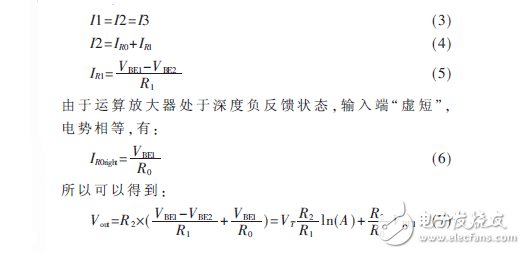

其中,VT具有正温度系数,VBE1具有负温度系数,则输出VRef的温度系数可以调整到接近零。

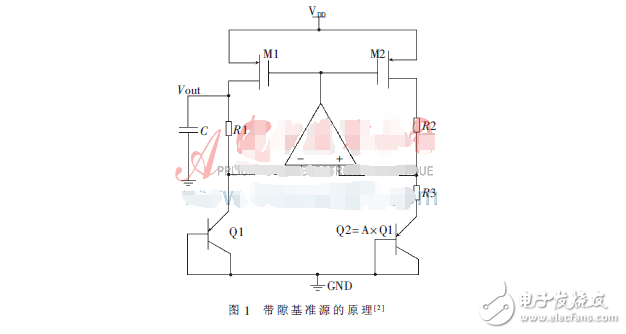

cmos带隙基准源设计电路为了得到较低的输出电压,在两个晶体管支路上分别并联一个电阻,根据此原理,设计电路图[3]如图2所示。

三个PMOS管为同样宽长的MOS管,均处于饱和工作状态,根据镜像原理有:

由式(7)可以看出,调节R2/R1与R2/R0的值,就可以得到零温度系数的电压输出值。虽然电阻本身也具有温度系数,但在此电路中,输出电压只与电阻之间的比值有关,所以电阻的温度系数对输出的影响很小。

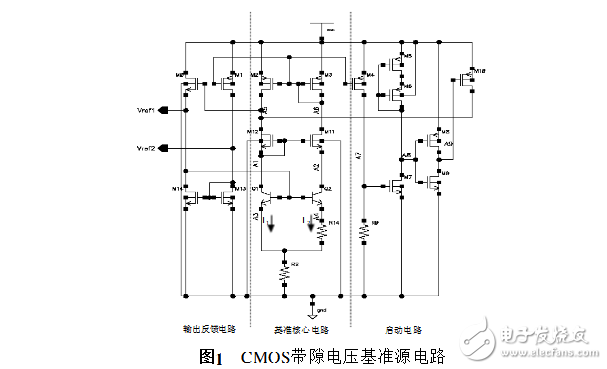

CMOS带隙基准电压源设计所设计Bandgap主要由启动电路,基准核心电路,输出反馈电路构成,以下分别予以讨论。

启动电路

为了使电路可以稳定工作,需要一个启动电路来使电路摆脱每个管子都关断的零工作状态。在图1中,当电路处于零工作状态时,M5 、M6导通,在电源电压作用下,使M9、M8组成的反向器导通,从而使M10开启,使电路回到正常的工作状态;电路正常工作以后,由于M4管子W/L大于M1、M2、M3,因此其跨导大,留过的电流大,从而使M7导通,将M10的栅极电压拉高关闭启动电路,进而使整个电路都处于导通状态,完成整个电路的启动工作。

基准核心电路

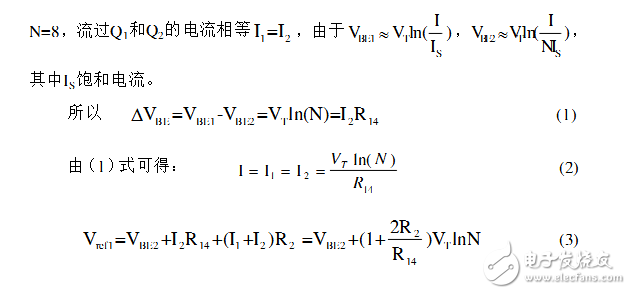

基于一次温度补偿技术,基准核心电路中, 晶体管Q1、Q2为使用标准CMOS工艺制造的NPN纵向三极管(BJT)。Q2和Q1的发射极面积的比为

设计中集电极采用带有源电流镜的差分对电路,这是一种与电源电压无关的结构。该电路与双极晶体管Q1和Q2结合得到与绝对温度成正比的偏置电流。假设M11的源极所带负载为Ra,Ra减小了M11上流过的电流,因此有:

无关,但仍是工艺,温度的函数。

输出反馈电路

该基准提供了Vref1,Vref2的两个输出,Vref1是与电源电压,温度,工艺无关的带隙基准电压输出,为其他电路提供一个稳定的电压偏置。M相当于一个源极跟随器,M12,M13作为负载,选择适当的W/L使得Vref1输出稳定。同时,流过M0的饱和电流中一部分反馈给双极晶体管的基极,作为正确的电流偏置。Vref2则是用于镜像复制电流,对温度,电源电压变化要求不高。

电路模拟和仿真结果

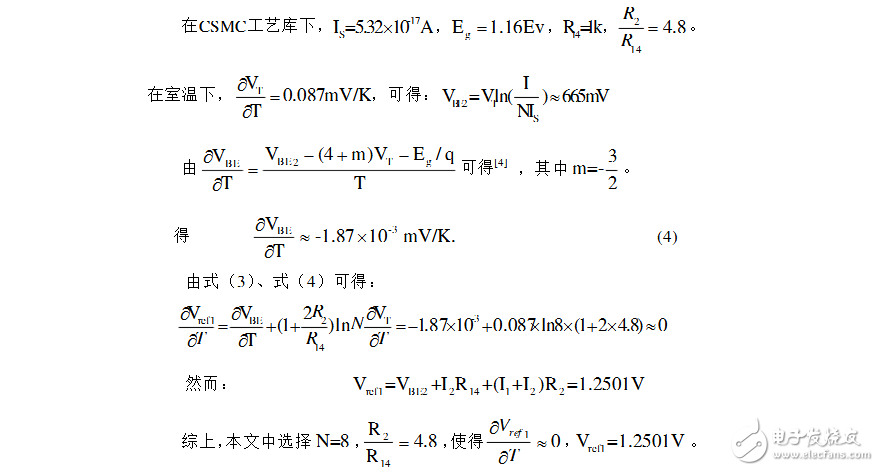

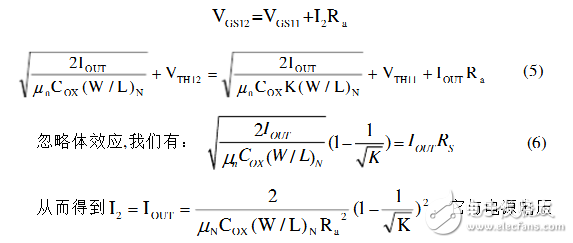

基于0.5 um CSMC工艺模型,用Cadence的Spectre仿真工具对该带隙基准电压源电路进行了温度扫描和电源抑制比的模拟仿真。温度范围为-40℃~80℃,电源电压范围为2V~5V。在0.5 um CSMC工艺tt/restypical/captypical/biptypical模型下的仿真所得结果为:温度系数可达45.53×10-6/℃。

由图3仿真结果表明:在-40~80℃范围内,带隙基准电压源输出电压的温度系数γTC = | (1/ V REF1 ) (ΔV REF /ΔT) | =45.53×10-6/℃。

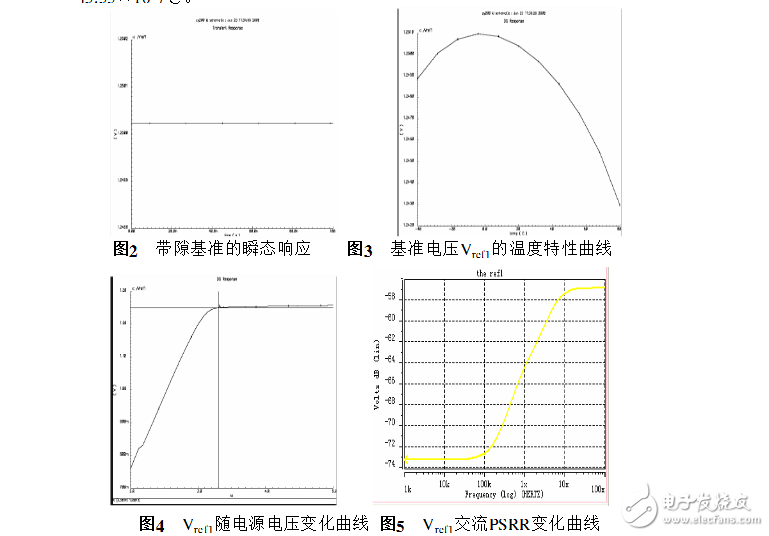

由图4可以看出,基准电压Vref1在3.3V-3.6V之间随电源电压变化很小,当电源电压大于3.6V,基准电压Vref1基本保持在1.25V左右。

由图5可以看出,低频时输出Vref1电源抑制比最低可达-73.3dB,在100 Hz 内PSRR 《 -72dB,之后逐渐下降,显示了电路在低频下具有良好的电源抑制能力,高频下也有接近-59dB的电源抑制能力。

欢迎分享,转载请注明来源:内存溢出

微信扫一扫

微信扫一扫

支付宝扫一扫

支付宝扫一扫

评论列表(0条)